Hammerがインテルに与えた衝撃は大きかった

Hammerの発表がインテルに及ぼしたインパクトは、かなり大きかっただろうと想像できる。2002年の時点では0.13μmプロセスの「Athlon XP」が健闘してはいたものの、動作周波数の差でNetBurstベースの「Pentium 4」が有利に推移していた。また2プロセッサー構成が限界で、しかもいろいろと不具合があったりしてなかなかサーバーマーケットへの浸透が図れなかったAthlon MPを尻目に、Xeonは着々と売り上げを伸ばしていた。

しかし前ページのHammerのベンチマークの結果を見る限り、IPC(Instruction Per Cycle)が大幅に改善して、しかも動作周波数2GHzあたりまでの製品が“当初から”投入されると見込まれた。このとおりなら、デスクトップ市場がかなり厳しい戦いになると予想された。

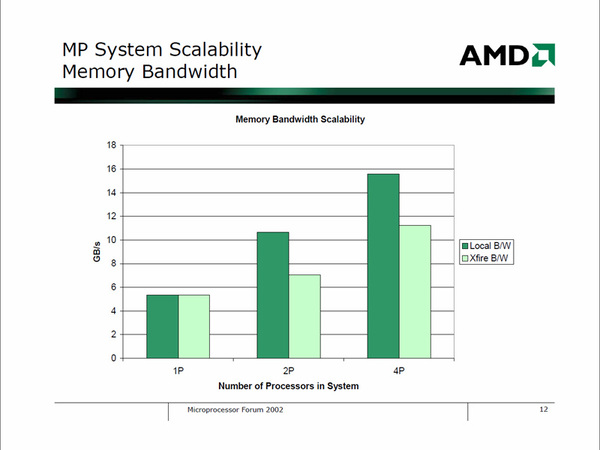

またHammerのメモリー帯域も、Xeonにとっては非常に脅威となる話であった。Xeonの場合は共有バス方式だから、1プロセッサーだろうが4プロセッサーだろうが、メモリーの帯域には一切差がない。むしろ4プロセッサーにするとFSBを遅くしないと間に合わなくなるから、むしろメモリー帯域は減る。帯域を増やすなんてことはまったくできない。

反応はすぐに現れた。インテルは2002年11月、突如として「Northwood」コアのPentium 4を小改良。Hyper Threading Technologyを有効にすることで、IPCの向上を図った。続く2003年4月には、それまで533MHzだったFSBを、(次の667MHzを飛ばして)800MHzまで引き上げることにした。これに合わせて「Intel 865PE」や「Intel 875」といった新チップセットも投入される。

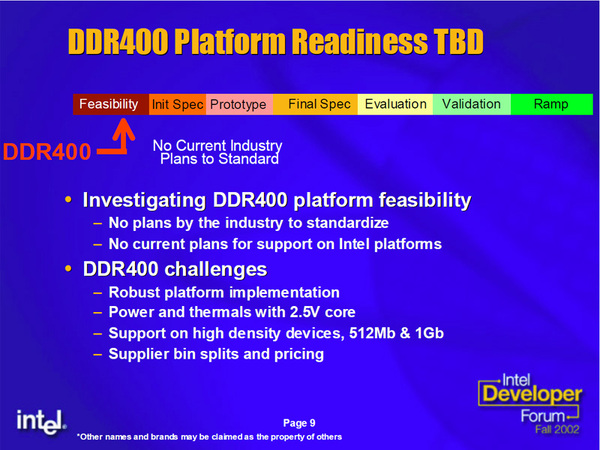

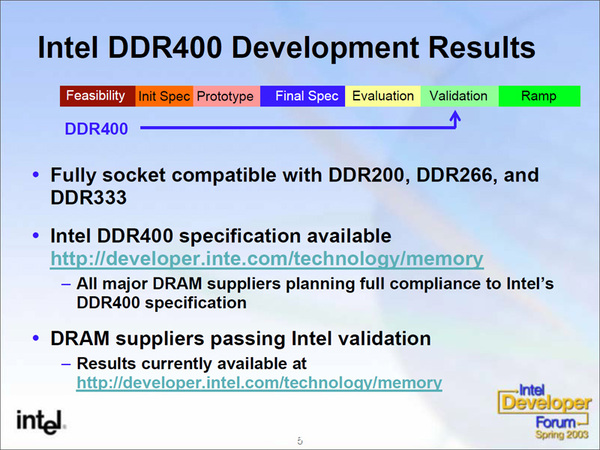

このIntel 865PE/Intel 875は、DDR-400×2という構成で800MHz FSBに対応することになった。しかし2002年9月時点でのDDR-400は、「まだFeasibility Study」、つまり「適合性を調査している」レベルということが、当時のIntel Developer Forum(IDF)2002で明らかにされている。ところがその半年後に開かれたIDF Spring 2003では、いきなりValidation(実機での検証)まで飛んでいた。

通常はFeasibilityに続けて、「Init Spec」(初期スペック策定)、「Prototype」(試作品の製造とこれによる検証)、「Final Spec」(最終的なスペック策定)、「Evaluation」(最終スペックの評価と検証)を経て、Validationに移る。通常なら最低でも1年、下手をすると2年近くかかるプロセスを半年足らずで済ませてしまうあたり、いかにインテルがDDR-400の策定を急いだのかがよくわかる。

これは少しでもメモリー帯域を引き上げることで、Hammerベース製品との性能ギャップを縮めようというインテルの努力の結果である。もちろんこれと並行して、次世代Pentium 4である「Prescott」の開発を急いだことも想像に難くない。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ