この連載の第1回はインテルのプロセッサーロードマップであった。第1回ではCore 2からスタートということで、それ以前のプロセッサーについては触れていなかった(第22回でも多少触れている)。1年以上延々とロードマップを書き続けて、やっと一巡した感があるので、今回からしばらくは古い製品をまとめて解説していきたいと思う。

i4004から始まったインテルプロセッサー

i8080でx86の基礎が固まる

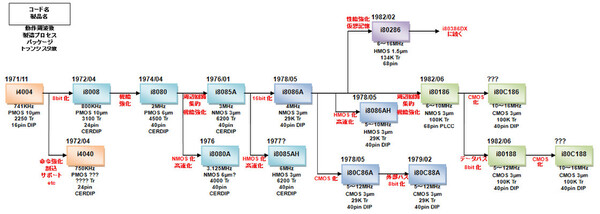

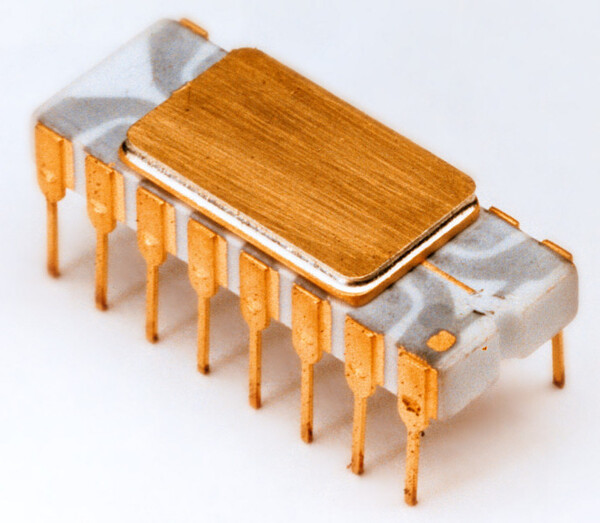

1971年に登場した、インテル最初のプロセッサーである「i4004」については、聞き覚えのある方も多いだろう。当時ビジコン社から出向の形でインテルに出向いた嶋 正利氏が設計に携わった、ということでも有名である。i4004は4bitのCPUで、アドレス12bit/データ8bitながら外部バスは4bit幅で、これを時分割多重で出力するという、ある種ものすごい設計になっている。

ここまでしたから16ピンDIPのパッケージで収まったとも言えるが、逆にそのため性能は恐ろしく低かった(大雑把に言えば0.03MIPS)。とは言え世界初のワンチップマイクロプロセッサーでもあった。

このi4004をベースに、命令数やレジスターなどを増やして性能を改善したのが「i4040」だ。発表そのものは1972年ながら、製造は1974年からとなっている。性能を改善と言っても、周辺回路はi4004のものをそのまま使えるように配慮したためか(4040で新規に追加されたチップもある)、外部バスは4bitのままである。

このi4040とは別の方向性でi4004を強力にしたのが、やはり1972年に登場する「i8008」である。このi8008もi4004と似て、CTC(Computer Terminal Corporation)という企業との共同開発によるものである。最終的にi8008は、CTCの製品には利用されなかったが、これをインテルは外販することにした。使いにくさはi4004によく似ていたが、外部バスは8bitとなり、性能もi4004のほぼ倍となっている。

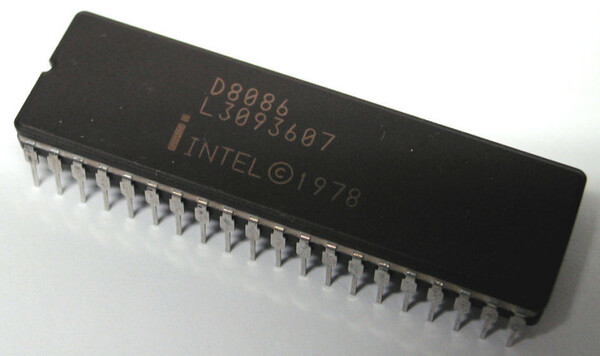

これを改良して使いやすくするとともに、性能を引き上げたのが、1974年に発表された「i8080」である。命令セットはi8008の上位互換となっており、x86の元になる命令セットはここで規定されたことになる。当初はPMOSプロセスで製造されたi8080だが、1976年にはNMOSプロセスに切り替わった「i8080A」が登場し、やや高速動作が可能になっている。

このi8080は、NECなど数社にセカンドソース供給された。例えばNECからは「μPD8080」として発売されている。またそれ以外にも、互換品が多く出回った。その代表例が、米ザイログの「Z80」である。

ただ、i8080/i8080Aではプロセッサーとは別に、さまざまな周辺回路を用意する必要があった。そこで一部の周辺回路の機能を内蔵するとともに、一部命令を強化したのが1976年に登場する「i8085A」である。その後、恐らく1977年には、プロセスをHMOS※1に切り替え、6MHz動作を可能にした「i8085AH」も登場する。

※1 NMOSの一種だが、「Depletion-mode」というFETの動作モードを使う方式。通常のNMOSよりもやや高価格だが、より高速に動作する。

これに続いて、1978年にはi8080/8085の上位互換である16bit CPU「i8086A」が登場する。この8086の場合、NMOSとHMOS、CMOSの3種類の製造プロセスによる製品が混在していた。NMOS版では動作クロックが4MHzどまりであったが、HMOS版では10MHz、CMOS版では最終的に12MHzに達する。

このCMOSベースのi8086をベースに、外部バス幅を8bitに削減することで周辺回路コストを節約したのが、「i80C88」である。ちなみに8088はCMOS以外にNMOS/HMOSの製品もあったらしいのだが、こちらの詳細は不明である。一番メジャーだったのはCMOSのもののようだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ