チップセット黒歴史が一段落してしまったので、しばらくは、やや違うロードマップを伝えていきたい。そこで今回からは、コプロセッサーの歴史をいくつか取り上げよう。

コプロセッサー、英語で書くとCo-Processorで、名前から判るようにProcessorの機能を補うものである。日本語では副プロセッサーなどと呼ばれた事もあるが、最近はコプロセッサーで話が通じるようだ。

副、というからにはもちろん正プロセッサーもあり、両方が対になって動くことでシステムを構成する。ただし「正プロセッサーはなにを処理し、副プロセッサーはなにを処理するか」はケースバイケースで決まる。

連載139回でお伝えしたRenditionの「Vérité V1000」の場合、正プロセッサーに当たるものは固定機能の描画パイプラインで、副プロセッサーが独自のRISC CPUだった。

あるいは(オンライン連載にない、書籍版だけの書きおろし記事で恐縮だが)MotorolaのMC88100の場合、「MC88200」というBus I/F兼キャッシュコントローラー兼キャッシュが別チップの形で用意されており、コンパニオンチップと分類すべきか微妙なところではあるが、一応MMUが入っているあたりは、コプロセッサーと呼べなくもない。

もっと巨大なシステムでは、「Intel iAPX 432」の場合、I/O処理などのために8086/8088プロセッサーを接続することになっており、システム的にはこれらはコプロセッサーの扱いとなっていた。つまり、システムの構成や定義次第で、どんなものでもコプロセッサーと扱われる可能性があるということだ。

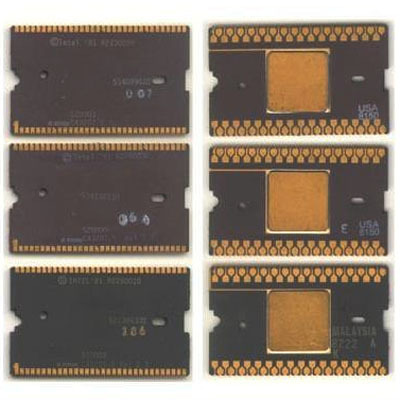

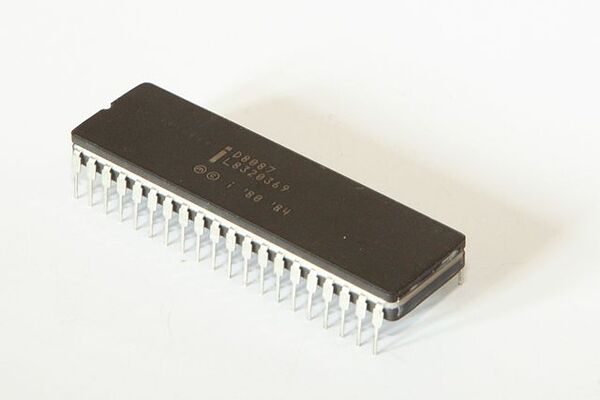

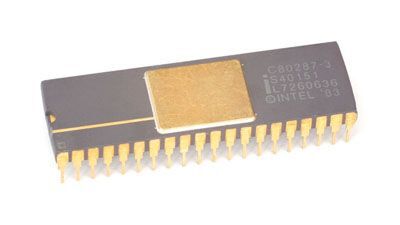

ただPCのマーケットでは、主にFPU(Floating Point Unit:浮動小数点演算ユニット)をコプロセッサーとして扱うことが非常に多い。事実、FPUは80486の世代になるまでは別チップで実装されていたし、その後もNexGenのNX586は、FPUとして「NX587」というチップをコプロセッサーとして別に必要としていた。なぜ別チップとして用意する必要があるのかを、今回は解説していきたい。

CPU回路の巨大化を防ぐために

FPUを別のチップとして供給

小数点の演算には、大別して固定小数点演算と浮動小数点演算の2種類がある。固定小数点演算の場合、10進数の表現は32bitだと

XXXX.YYYYY

で固定になる。小数点の位置はインプリメント次第で変更可能だが、普通は

0.YYYYYYYYY~XXXXXXXX.Y

という範囲までである。32bitでは有効桁数が9桁ほどしかないので、整数部の最大値はどんなにがんばっても8桁どまりになる。9桁をフルに使うと小数でなくなってしまうからだ。これが64bitになると有効桁数が18桁に増えるので、

0.YYYYYYYYYYYYYYYYYY~XXXXXXXXXXXXXXXXX.Y

までの表現が可能になるが、場合によってはこれでも足りないことがある。他方浮動小数点の場合、10進数の表現は32bitだと

0.YYYYYY×10ZZ

で、有効桁数が若干減る代わりに、-10-126~10127という非常に広い範囲の数字を表現できる。同様に64bitでは

0.YYYYYYYYYYYYYYY×10ZZZ

となり、-10-1022~101023までが表現可能となる。小数部の有効桁数も15桁まで広がるので、科学技術演算であっても、それなりの精度で演算できる。

こうした特殊なデータフォーマットを扱うことの必要性そのものは昔から知られていたものの、問題はこれを実現しようとするとCPUの回路が巨大化してしまうことだ。特に乗算/除算の処理や、Sin/Cosやexp/logといった特殊関数の演算回路がかなり大きくなってしまう。

実際、後述する「Intel 8086」と、そのFPUである「Intel 8087」を比較した場合、8086のトランジスター数は2万9000個なのに対し、8087は4万5000個とFPUのほうがサイズが大きくなっている。これを1つのパッケージにすると、当然ダイサイズも大きくなり、歩留まりが悪くなるため、価格も引き上げざるを得ない。

かといって、8086を購入したユーザー全員がFPUを必要としたかというと、そういうわけではなく、大多数のユーザーはFPUを使っていなかった。したがって、FPUを別チップに分けるのは経済合理性の観点から言っても、生産の容易さからいっても理にかなっている。

余談であるが、浮動小数点数演算の標準をまとめたものに、IEEE 754がある。このなかでは基本形式や交換形式、丸め規格、演算、例外処理など浮動小数点演算に求められる要素を規格化したもので、x86系以外にも多くのCPUやFPUがこのIEEE 754に準じた形でFPUを構成している。

IEEE 754の基本形式のうち2進数に関して、当初は16bit(半精度)、32bit(単精度)、64bit(倍精度)、128bit(4倍精度)の4種類のフォーマットが予定されていたが、8087は最大でも80bit精度しか搭載しない。

これは128bitをフルに実装すると回路規模が大きくなりすぎてしまうため、80bitという中間的な桁数を認めるようにIEEEに強く働きかけた結果である。ただこの結果として、4倍精度をサポートするFPUは非常に少なくなってしまい、ほとんどのものが80bit精度の実装で済ませてしまっているあたりは、先例を作った8087の罪は重いと筆者は考える。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ