前回では「バス」の歴史について大雑把に解説したので、今回はPCの基礎を築いたと言える、「XT Bus」と「ISA Bus」の詳細について解説したい。

XT Busを拡張して生まれたISA Bus

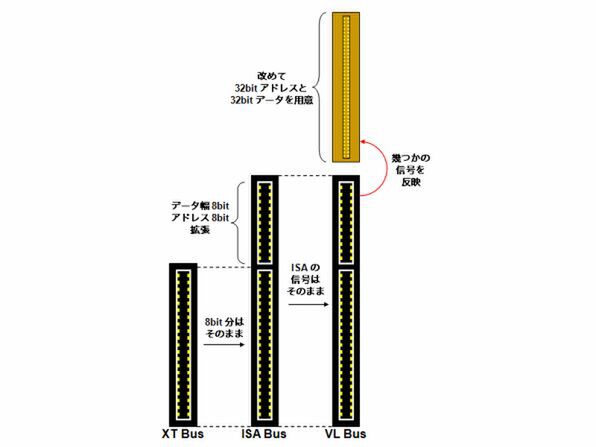

まずは話をわかりやすくするために、3種類のバスの関係を図1に示す。大元になったのは、「IBM PC/XT」で採用されたXT Busである。このXT Busをそのままに、アドレスとデータをそれぞれ8bitずつ拡張して、合計で16bitのバスとしたのがISA Busである。

一方の「VL Bus」(次回解説する)は、ISA Busとはまったく別に、改めてアドレスおよびデータを32bit幅で用意したバスである。その意味ではVL Busとは、図1では黄色いコネクターで拡張された32bit Busのことだけをいう。VL Busは単独では動作できないので、必ずISA Busか「EISA Bus」と連携をとる必要がある。そのため図1のように、「VL Bus+ISA Bus」もしくは「VL Bus+EISA Bus」という形で実装されることになった。

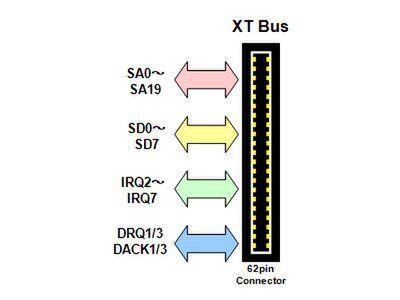

XT Busに話を戻そう。XT Busは「i8088」をベースとしたPC向けバスになる(図2)。そのためデータバスは8bit幅である。ただし、i8088は最大1MBのメモリー空間を持つので、これをサポートするためにアドレスバスは、1MB分にあたる20bitが用意されている(SA0~SA19)。

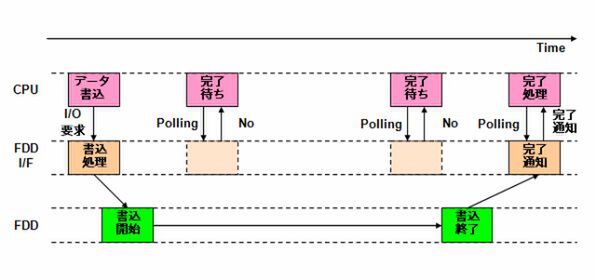

「IRQ2~IRQ7」とは何かと言うと、割り込み信号である。これを説明するにはI/Oの基本的な説明をしておく必要があるだろう。図3は、CPUからFDDに書き込んだ場合の、処理の流れである(HDDも同様)。一連の流れを箇条書きにするとこうなる。

- ① CPUはFDD I/Fのコントローラーに対して「I/O要求」を出す。

- ② これを受けたFDD I/Fは、FDDに対して書き込みをする。

- ③ FDDは書き込みを開始し、終わったら「完了通知」をFDD I/Fに返す。

- ④ FDD I/FはCPUに「完了通知」を返す。

- ⑤ CPUは完了通知を受け取り、ファイル書き込みを完了する。

完了通知が来るまで待つのは、もし書き込みに失敗したら再書き込みするなり、書き込み自体が失敗したというエラー処理をするためだ。書き込み要求を出したらそれで終わり、というわけにはいかない。そこで問題になるのは、「CPUはいつ書き込み完了を知るか」である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ