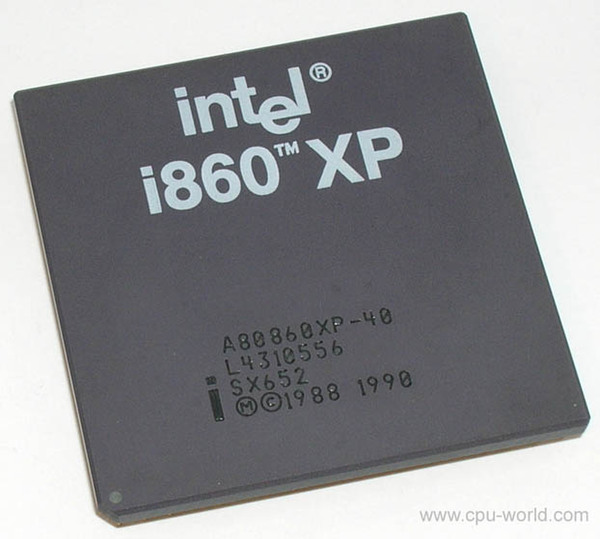

写真提供 CPU World

CPU黒歴史編の3回目は、インテルのRISC CPUである「i860」を取り上げたい。型番が同じ“860”なので、Xeon向けにデュアルプロセッサー構成をサポートしたDirect RDRAM対応のチップセット「Intel 860」などと間違えやすいが、まったく別の製品である。

CISC vs RISC論争華やかなりし頃

インテルが作ったRISC CPU

i860について解説するには、前回紹介した「iAPX 432」の失敗が明らかになりつつあった、1980年初頭の状況から始める必要がある。当時のCPU市場は、RISCプロセッサーが台頭してきた時期に当たる。

当時はスタンフォード大学で「MIPS」プロジェクトが開始された頃。1984年にはMIPS Computer Systems社が設立されて、1985年に最初のCPU「R2000」が登場する。同じ1985年には、Sun Microsystemsが最初の「SPARC」チップを開発したほか※1、IBMは1981年に「ROMP」(Research Office Products Division Micro Processor)を完成させるなど、いわゆる「CISC vs RISC論争」が活発だった時期でもある。

※1 商用向けに出荷されたSPARC V7ベースの製品は1987年登場。

おさらいしておくと、「RISC」とは「Reduced Instruction Set Computer」(縮小命令セットコンピューター)の略で、要するに命令セットを簡単にすることでCPUの内部構造を簡単にして、これにより高速動作をさせることで性能を引き上げようという考え方だ。代表例が、上で挙げたMIPSやSPARC、ROMPや、ROMPの技術を元に作られたPOWER/PowerPC系のアーキテクチャーのCPUである。

これと対比するのが「CISC」で、こちらは「Complex Instruction Set Computer」(複合命令セットコンピューター)の略である。代表例はインテルのx86やモトローラの「6800、68000」などで、命令数が非常に多いタイプのCPUである。前回取り上げたiAPX 432は、ある意味「CISCの頂点を極めたプロセッサー」とも言える。

今でこそ「CISC vs RISC」の優劣を論じる論争は無意味になっているが、この当時はそれなりの説得力があった。背景にあるのは、当時の半導体製造技術が今よりずっと劣っていたことだ。トランジスターの性能は低かったし、ダイに搭載できるトランジスターの数もずっと少なかったから、複雑な命令を扱えるようにするためには、ある程度性能を犠牲にせざるをえなかったからだ。

RISCは命令が簡単で、しかも命令にはいろいろ制約がある。例えば、ほとんどの命令はメモリーをアクセスできないので、メモリー内のデータにアクセスするためには、まずメモリーからレジスターへのロードを行なう必要がある。だが、これはコンパイラーがうまく対処すれば解決できる、という割り切りが背景にあった。

当時はインテルとしてもこうしたトレンドは無視できないものであり、ましてやiAPX 432が華々しく失敗したこともあるので、挽回する必要があった。そこでRISCの考え方を全面的に取り入れて、ゼロから新規に設計されたのがi860であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ