4回に渡るインテル編の最後は、サーバー向けプロセッサー。要するにXeonの話題で締めくくろう。まずはXeonの詳細に入る前に、Xeonラインナップの基礎知識を説明したい。

3ラインナップのXeon

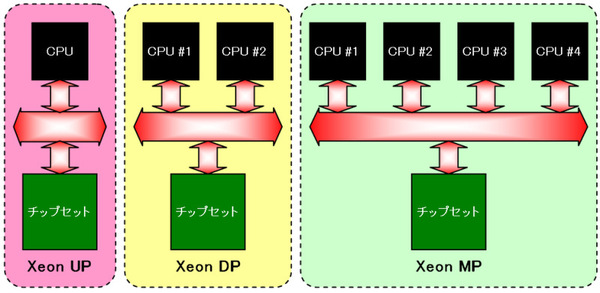

バス構造が性能のボトルネックに

インテルはXeonという1つのブランドの下に、大別して3種類の製品をラインナップしている。小規模サーバーや組み込み向けに使われる、1(Uni)プロセッサーXeon(通称Xeon UP)。一番ボリュームの大きい2プロセッサーXeon(Xeon DP)、それとハイエンド向けに4プロセッサー“以上”の構成をとるXeon(通称Xeon MP)の3種類だ。ほとんどの場合、Xeon UPはデスクトップ向けのプロセッサーをそのまま流用する形だが、Xeon DPでは2プロセッサー用となり、更にXeon MPではスペシャルな構造のものが特に投入されることが多い。

これは、インテルCPUのバス構造に起因する問題である。ごく最近のNehalem以前のインテルCPUは、すべて共有バスの構造を取っていた。図1はこれを判りやすく示したものだが、バスそのものは最大で「4つのCPU+1つのチップセット」の5つのデバイスを接続できるように設計されており、あとは構成次第でいくつまでCPUを接続できるかを、調整できるようになっている。

チップセットの側もこれに対応した構造になっていることが多い。デスクトップ用でありながら、デュアルCPUに対応したマザーボードも過去にいくつか存在しているほどだ。ただインテルは、こうした2P/4Pの構成を製品差別化の重要な要素と捉えており、例えば微妙にCPUソケットの形状を変えたり※1、マザーボードベンダーには、「Xeon DP用ソケットを搭載したXeon MP構成のマザーボード」を作らないよう“強力に指導する”といった技を駆使してきた。それはともかく、問題はシステム性能が向上する中で、共有バスという方式そのものがボトルネックになってきたことだ。

※1 例えばXeon MP用のマザーには、Xeon DPやXeon UPのCPUが刺さらないようにする。

問題のひとつは周波数。Pentium III世代の「P6バス」の時代は、バスの周波数は66/100/133MHzと比較的低速だった。それでも133MHzが使えるのはUP/DP構成までで、MP構成では100MHzが上限だった。ひとつのバスに5つもデバイスが乗っていると、高速動作時には信号波形の乱れなどが無視できないレベルになるようだ。

この制限は、P6バスを継承したPentium 4世代から現在まで続く「P4バス」にも引き継がれた。P6バスとP4バスの大きな違いは、データレートとベースクロックの組み合わせにある。P6バスはデータレートとバスのベースクロックは同一で、例えばベースクロックが100MHzならば、データもやはり100MHzで転送された。P4バスではデータレートはバスのベースクロック×4、つまり4倍速で転送される。しかしこの結果、速度の上限はさらに厳しくなった。

実際、Core 2の世代ではベースクロックが400MHz(データレート1600MHz)まで上がったのだが、Xeon MP向けシステムのベースクロックは266MHz(データレートは1066MHz)に留まっている。本来ならばXeon MPこそ大量のデータを取り扱うために、データレートをXeon UPやXeon DPより引き上げないといけないのだが、共有バスを使っているためにそれが不可能となっている。このギャップを埋めるため、Xeon MP向け製品はしばしば、大量の3次キャッシュを追加搭載する形で性能を補ってきた。

(次ページへ続く)

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ