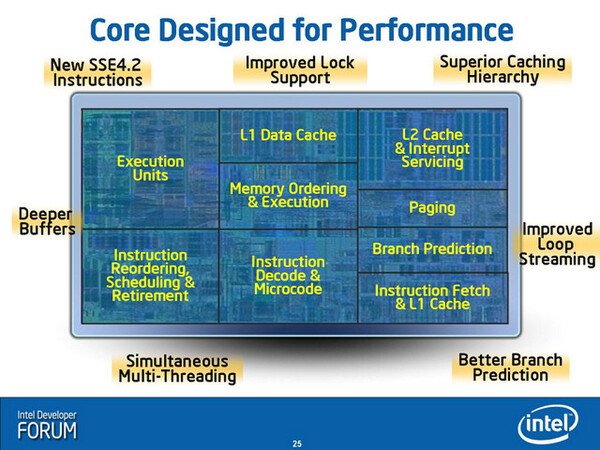

IDF上海の技術セッションにて、米インテル社の次世代CPUの「Nehalem」(ネハレム、ネヘレム)の内部アーキテクチャーの解説が行なわれた。Nehalemは、現行のPenryn(ペンリン)世代のCore 2 Duoプロセッサーと比べると、マイクロアーキテクチャー自体に劇的な変化はないが、地道な改良によりパフォーマンスが向上している。

特に大きな変更点は、CPUのハードウェア構成面にある。基調講演のレポート(関連記事)と重複するが、IDFの資料を元に、Nehalemの姿を明らかにしていこう。

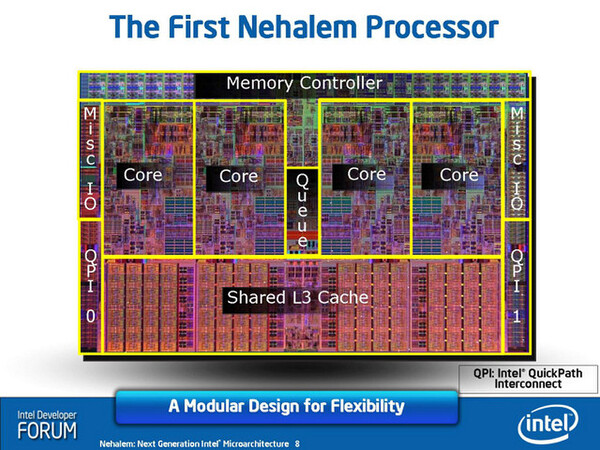

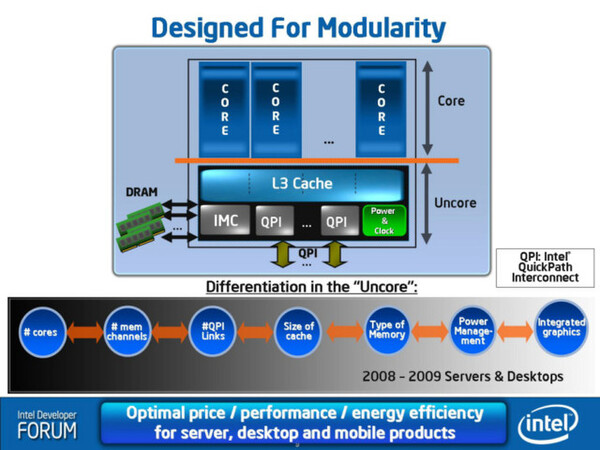

Core 2 Duoは既存のCPUコアを1パッケージにまとめることで、マルチコアCPUを構成している。Nehalemはこれとはまったく異なる。新しくCPUをデザインしなおし、CPUの機能ブロックをそれぞれモジュール化している。これにより、CPUコアの増減が容易になる。

Penryn世代のCPUは、ひとつのCPUダイに2つのCPUコアが実装されている。そしてPenryn世代の4コア製品は、2つのPenrynをひとつのCPUパッケージに収めた形になっている。6コアの「Dunnington」なら、3つのCPUを1パッケージ(2コア×3つ)にまとめているわけだ。またPenrynでは、CPUダイ間の通信は既存のシステムバス(FSB)で行なわれている。一方のNehalem世代では、CPU設計を改めて、CPUコアを1個単位で追加できる。

当初リリースされるNehalemは、多くても1パッケージで4コアとなっているが、設計次第で5コアや6コアのNehalemを作ることも可能だ。しかし同社の級副社長兼デジタル・エンタープライズ事業本部長のパット・ゲルシンガー(Patrick P.Gelsinger)氏によれば、「パフォーマンスを考えると、Nehalem世代では2~4~8コアになるだろう。現状では、中途半端なCPUコア数のNehalemをリリースする考えはない」と述べ、3コアの「Phenom X3」を供給する米AMD社とは、異なる路線に進むことを示唆した。

インテルでは、ノートパソコンとローエンドのデスクトップPCにはデュアルコアのNehalemを、メインストリームPCとハイエンドのデスクトップPC、サーバー&ワークステーションは4コアの製品を、そしてサーバー向けにオクタル(8)コアの製品を投入する予定だ。32nmの製造プロセスを使用する2009年登場予定のCPU「Westmere」(ウエストメア)では、8コア以上を目指すという。

キャッシュメモリーに特徴のあるNehalem

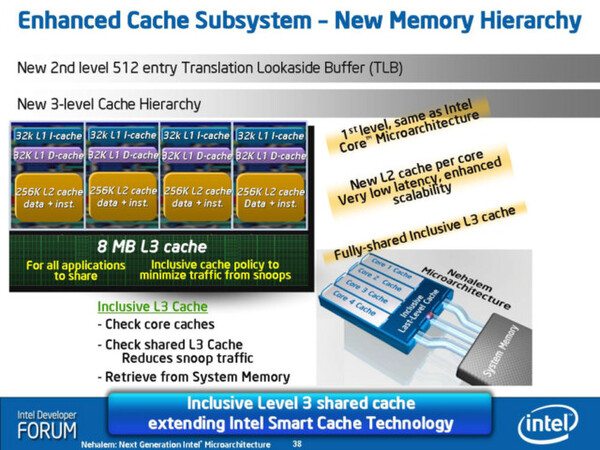

Nehalemの大きな特徴のひとつが、CPUのキャッシュメモリーを3段階搭載した点にある。各CPUコアは1次~2次キャッシュまでを個別に持ち、3次キャッシュはすべてのCPUコアが共有している。CPUに最も近い1次キャッシュは、データと命令キャッシュの2つで、それぞれが32KB。2次キャッシュはCPUコアごとに256KB。3次キャッシュは共有で、約8MBを持っている。

ただし、3次キャッシュの容量はCPUコア数によって増減する。8コアCPUでは、8MBの3次キャッシュでは少なすぎるし、2コアCPUでは多すぎる。製品バリエーションにより異なることになるだろう。1次~2次キャッシュメモリーの容量は、CPUコアが増減しても変わらない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります