ロードマップでわかる!当世プロセッサー事情 第803回

トランジスタの当面の目標は電圧を0.3V未満に抑えつつ動作効率を5倍以上に引き上げること IEDM 2024レポート

2024年12月23日 12時00分更新

電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ

性能は0.65V動作のトランジスタの半分程度まで引き上げるのが目標

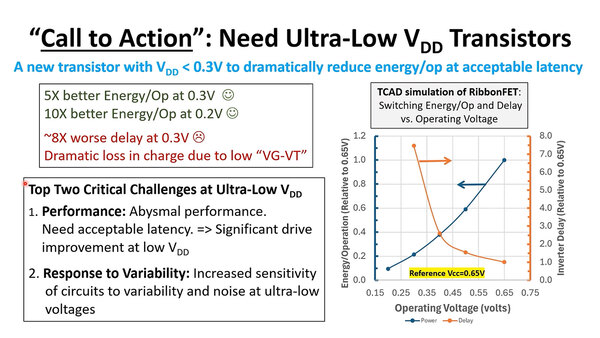

ただ、2030年を目指すにあたっては、単に面積の縮小だけでなく、消費電力と放熱の問題も解決する必要があるとする。まず消費電力にからむ話で、とにかく電圧を下げないことには消費電力が下がらないのだが、電圧を下げると同時にトランジスタの速度も大きく落ちてしまう。

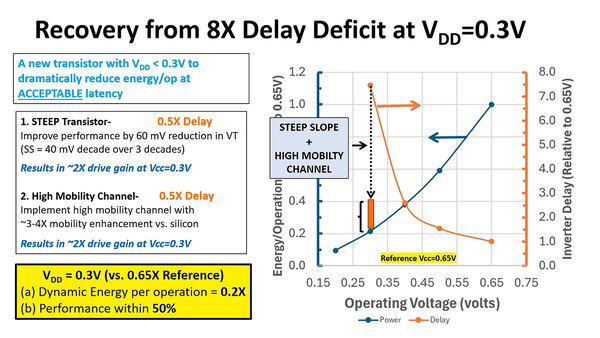

0.6Vで動作するトランジスタを0.3Vまで落とすとエネルギー効率は5倍に向上するが、トランジスタのスイッチング速度が8分の1になってしまう。

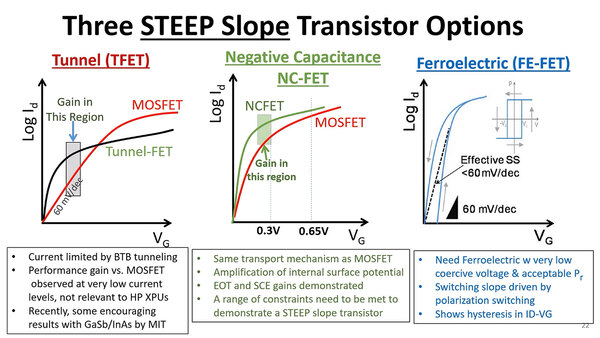

これを改善するトランジスタの構造をSteep Slope Transistorとして各社さまざまな技法を検討している。

トランジスタそのものが遅くなることそのものは仕方ないとして、その遅くなる程度を許容範囲内に抑えたい、というのが現在の目標になっている。また、電荷の移動速度を高速化する技法を併用することで、実用につなげたいというわけだ

そのSteep Slope Transistorの候補して現在はTunnel FET(トンネル効果を利用したトランジスタ)、Negative Capacitance FET(NC-FET:強誘電薄膜をゲート絶縁膜に利用することで、負の電界容量を持つ状態を作り出し、これを利用したトランジスタ)とFerroelectric FET(同様に強誘電体膜をゲート絶縁膜に用いる技法だが、Negative Capacitance FETとは異なる)の3つを候補として挙げている。

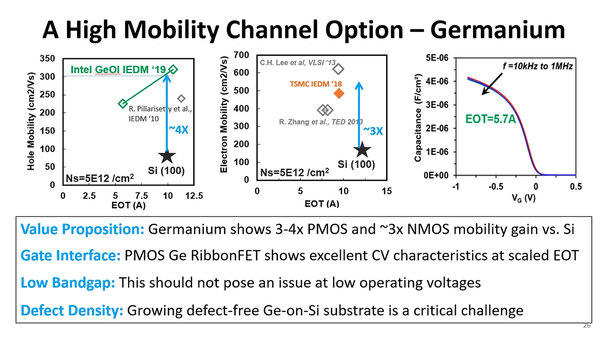

一方チャネルの電荷移動量の改善に関しては、シリコンをGe(ゲルマニウム)に変更することで、大幅に性能が改善される(PMOSで3~4倍、NMOSで3倍)ために有望である、としている。

これを組み合わせた、1つのビジョンが下の画像だ。電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ、性能は今の0.65V動作のトランジスタの半分程度まで引き上げることを目指している。

ただこれはトランジスタレベルでの改良であり、実際にはチップにする際にまた別の配慮が必要であるが、それは別の招待講演で説明されたので、次回はそちらをご紹介しよう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ