ロードマップでわかる!当世プロセッサー事情 第790回

AI推論用アクセラレーターを搭載するIBMのTelum II Hot Chips 2024で注目を浴びたオモシロCPU

2024年09月23日 12時00分更新

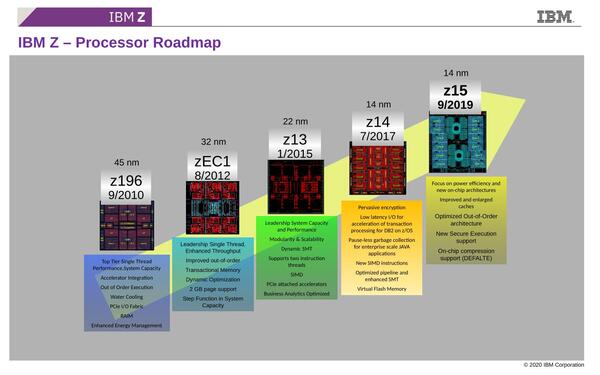

Hot Chips第3弾は、IBMのTelum IIである。これはIBMのzシリーズの系列のプロセッサーとなる。IBMのzシリーズは以前連載502回で取り上げたが、高可用性/高信頼性を最大の特徴とするメインフレーム向けプロセッサーのシリーズである。連載502回ではz14までのラインナップを紹介したが、2019年にz15プロセッサーが発表された。

10進演算がある珍しいzシリーズ

2019年にz15プロセッサーを発表

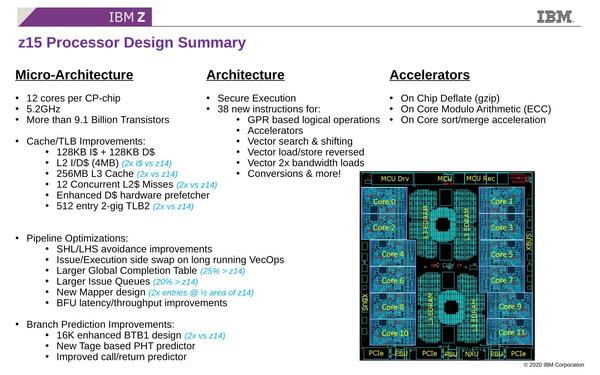

z14→z15はどちらも同じ5.2GHz動作であるが、コア数以外に細かな性能向上の工夫が凝らされている。

同じSamsungの14nmプロセスを使っており、コアのエリアサイズ最適化によって同じダイサイズで2コア増え、しかもL3を倍量にしたことになるが、さすがにL3もなにか工夫が凝らされたものと思われる。ちなみにz14は61億トランジスタ、z15は91億トランジスタと説明されている

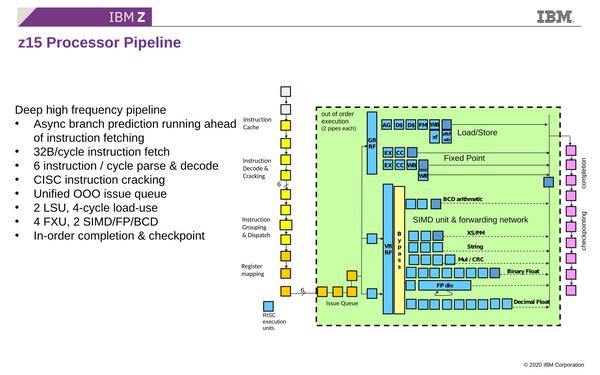

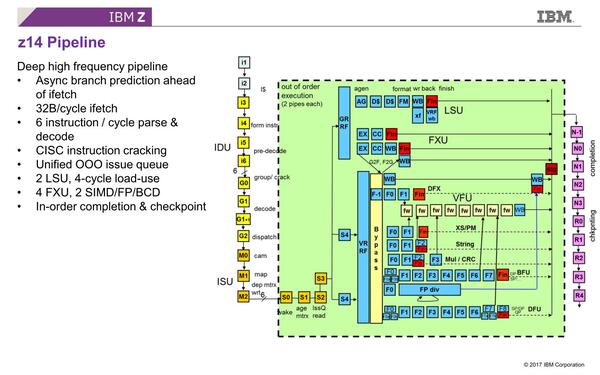

処理パイプラインの構造そのものは、細かな改良は当然いろいろあるにせよz14とz15はほぼ同じで、6命令/サイクルのデコードを持つフロントエンドに、ALU×4+Load/Store×2、FPU/Vector×6のバックエンドという構成になっている。z15がおおむねz14の延長にあることはおわかりいただけるだろう。

z14(とz15)は、同じパイプが2本づつになっているので、FXU(Fixed eXecution Unit)が×4という計算になる。どうもレジスタ書き込みのみ(CCのあとFinになる)とメモリー書き込み(CC→WB→Finになる)では別のパイプになっているようだ

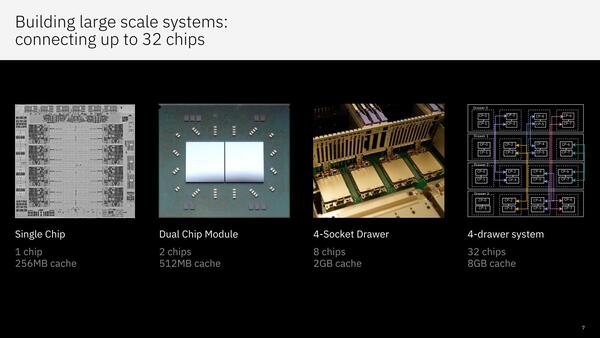

ちなみにシステム全体という意味では、z14では6つのCP(Central Processor)チップが1つのSC(System Controller)チップにつながっており、この7チップで1つのドロワー(要するにシャーシに収まるユニット)を構成する。

SCは言ってみればドロワー間を接続するためのI/Oチップみたいな扱いだが、その672MBのL4も内蔵されている。これに対しz15では4つのPU(Processor Unit:z14で言うCP)と1つのSCでドロワーが構成されているが、SCには960MBものL4が搭載されているという違いがある。

最大構成で言えば、z14の場合は24CP(つまり240コア)までサポートし、一方z15は20PUだがコア数で言えばやっぱり240コアになる。Xeonの8ソケット構成など問題にならないくらいの大規模なシステムが構築できる。

分岐予測を再設計したTelum

周波数はz15から据え置きでキャッシュを増量

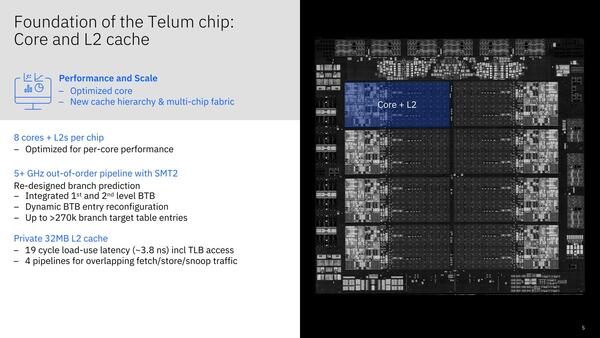

そのz15の後継として2021年に発表されたのがTelumプロセッサーである。Telumではややプロセッサーの方向性が変わった。まずチップそのものであるが、8つのコアから構成される。

おのおののコアの詳細は明らかにされなかったが、基本はz15までのパイプライン構造を踏襲しているものと考えられる。2スレッドのSMTというのもz13時代からずっと実装されている話で、このあたりは変わらない。

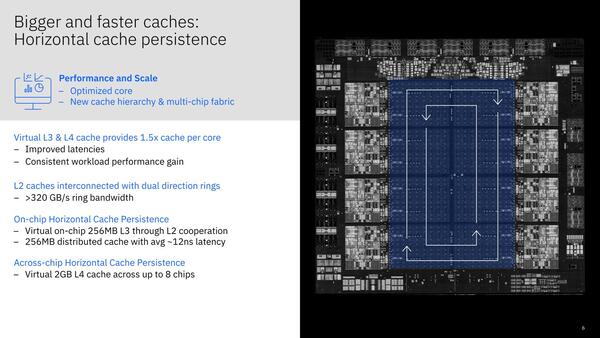

また動作周波数も5.2GHzで据え置きである。L3とL4は8コアで共通だが、コアあたりの容量は1.5倍になったほか、Virtual L3/L4が搭載された。このVirtual L3/L4は、以下の仕組みになっている。したがって、全コアが稼働中だとVirtual L3/L4は無効になる。

- 同一チップ内の非アクティブなコアのL2をL3として扱う

- 異なるチップ内の非アクティブなコアのL2をL4として扱う

Telumのダイそのものは7nmプロセスを利用しているとあって530mm2とそれほど大きくないが、実際には2つのダイを1つのチップに搭載している。

1つのドロワーには4チップが搭載されるので、1ドロワーあたり64コアという構成だ。システム全体では4ドロワー構成(32チップ:256コア)までのSMP構成が可能とされる。ちなみにシステム的には256コアでも、ユーザーが利用できるのは最大200コアに制限されているそうだ。

※お詫びと訂正:記事初出時、Telumの発表年に誤りがありました。記事を訂正してお詫びします。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ