Intel 3はIntel 4より300~500MHzほど動作周波数が向上

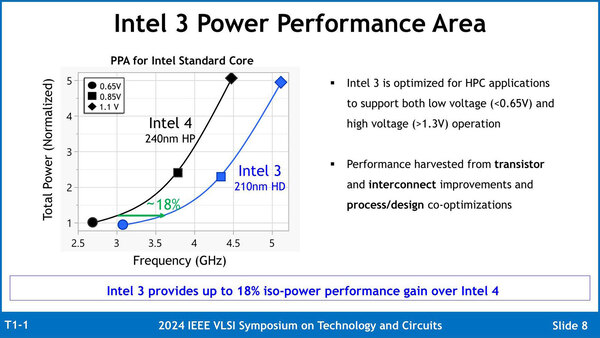

さてそのIntel 3の中身であるが、まずはStandard CellにおけるPPA Optimizationの結果が下の画像だ。同じ電力では300~500MHzほど動作周波数が向上するとしている。

Standard CellにおけるPPA Optimizationの結果。PPAとはPower・Performance・Areaのこと。この3つを同時に満足させるのは難しいので、通常はPerformance優先(PowerとAreaは大きくなる)か、Power・Area優先(Performanceは下がる)になるのだが、なにをどの程度優先するかのバーターは難しい

ただこれ、Intel 3の方は210nmのHD Libraryを使っていることに注意されたい。おそらく、HP Libraryでは動作周波数はさらに上がるが、Powerももっと増えるものと思われる。

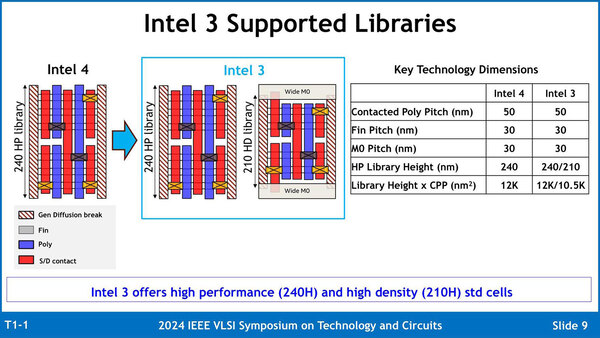

さきほども出てきた210nmのHigh Density Libraryと、Intel 4と同じHigh Performance Libraryの違いが下の画像だ。Gate Pitch(横幅:この図で言えば、2つのDiffusion Breakの間の距離)は変化ないが、240nmの方はPMOS/CMOSともに3 Fin構成なのに対し、210nmの方は2 Fin構成となっている。結果的にLibrary Hightが210nmに減ったわけだ。

HD LibraryとHP Libraryの違い。やや気になるのが、M0 Pitchは変わらない(30nm)としているものの、M0の配線幅そのものは太くなってるように見えることだ。これだと結局Libraryの密度そのものが上がらなくないだろうか?

これだけ見ていたら性能が向上する理由は理解できないのだが、2つ上の画像の右下にあるように、トランジスタとインターコネクトの改善で性能向上を果たしたとしている。その結果、Intel 4の3 Fin構成よりIntel 3の2 Fin構成の方が性能も上がってしかも省電力という特性につながったわけである。

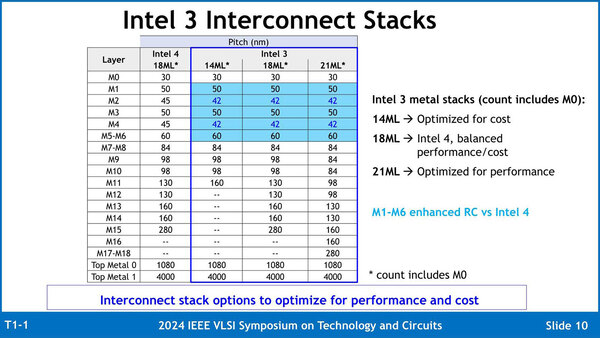

というわけで、そのインターコネクトについて。Intel 4では配線層が18層だったが、Intel 3では14/18/21層の3種類が用意される。この18MLがある意味標準的な位置付けとなるわけだが、レイヤーで言えばM2とM4が若干微細化されているのがわかる。

Intel 3では3種類のインターコネクトを用意。14MLは将来省電力版の、例えばスマートフォン向けSoCなどを製造する場合に利用することを想定しているのかもしれない。もっとも最近のArmのCPU IPやGPU IPが14層で製造できるのか? と言われると疑問で、このあたりもう少し具体的にアプリケーションを聞きたいところではある

またIntel 4の配線では、M1~M4がeCU(銅配線の外側にコバルトの薄膜を付けた構造)になっていたが、Intel 3ではこれがM6までに拡張されたほか、enhanced RCということでおそらくは抵抗を減らすなんらかの工夫がなされた模様だ。

もしもArrow Lake-Uが本当にIntel 3で製造されているとすれば、18MLあたりが使われるだろう。逆にXeon 6(特にGranite Rapids)は、21MLを使っているかもしれない。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ