RISC-V財団の創立メンバーは41社

活動資金を自前でまかなえる規模

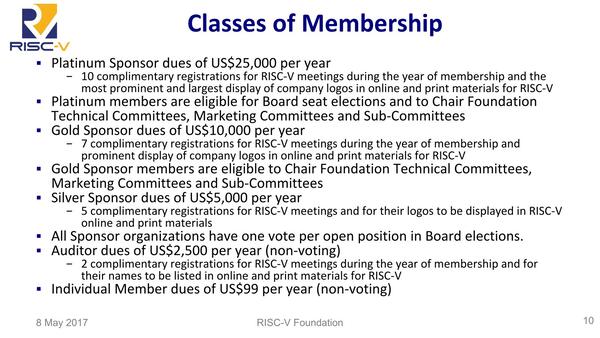

前回の続きとなる、RISC-Vプロセッサー遍歴の4回目をお届けしよう。2016年に入ると、RISC-Vの普及は加速していく。そもそもRISC-V Foundation(財団)の創立時点では、4種類(Platinum/Gold/Silver/Audit)+1(Funding)のレベルがあった。Platinum~Auditの各レベルの説明は下の画像になるが、要するに毎年2万5000ドル支払えばプラチナスポンサーとして取締役会に参加できるし、1万ドル支払えばゴールドスポンサーとなり、委員会の議長に就くことが可能である。年間5000ドルのシルバースポンサーではミーティングへの参加資格が得られる。PCI-SIGなどとよく似た、わりと一般的なシステムである。

Auditorは投票権がないが、ミーティングへの参加が可能である。ただこれに2500ドル払うなら、さらに2500ドル足してシルバースポンサーになる方がメリットが大きく、それもあって2016年7月の時点ではメンバーが2社しか存在しない

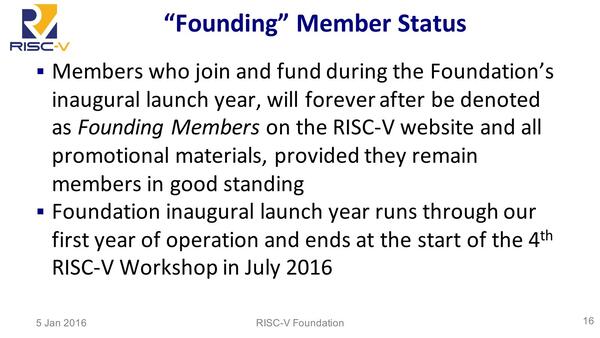

これとは別にFounding Memberという「ステータス」があるのだが、これは2016年7月までに出資した企業に与えられるもので、レベルは必ずしもプラチナである必要はない。

実際2016年11月のMember Directoryを見ると、41社がFounding Memberであることが示されており、例えば台湾のAndes Technologiesは2016年7月時点ではFounding Memberであるものの、Silverでしかない。ちなみに41社を並べると下表のようになっている。

| RISC-V財団の創立メンバー | ||||||

|---|---|---|---|---|---|---|

| グレード | メンバー | |||||

| Platinum | Berkeley Architecture Research、Bluespec、Cortus、Draper、Google、HPE、IBM、Mellanox、Microsemi、Microsoft、NVIDIA、Oracle、Qualcomm、Rambus、SiFive、WD | |||||

| Gold | AMD、BAE Systems、Esperanto Technology、Espressif、IDT | |||||

| Silver | Andes Technology、Antmicro、Blockstream、Codasip、ETH Zurich(チューリッヒ工科大)、Gray Research、IIT Madras(インド工科大学マドラス校)、Intrinsix Corporation、Lattice Semiconductor、lowRISC、Minima Processor、ROA Logic、Rumble Development Corporation、Runtime.io、Sur Technology、Syntacore、Technolution、VectorBlox Computing Inc. | |||||

| Auditor | ICT(中国科学院大学)、MIT CSAIL(MITコンピュータ科学・人工知能研究所) | |||||

この時点でインテルこそ名前を連ねていないものの、AMDやIBM、Qualcomm、NVIDIAなどのCPUメーカーに加え、Googleやマイクロソフトなどのソフトウェアベンダー、MellanoxやWD、IDTなどのメーカーまで参画しているのは、少なくとも第一歩としては大成功として良いと思う。またFounder Member以外でもMicronやNXPがともにプラチナで入っており、RISC-V Foundationの活動資金を自前でまかなえる目途が立ったことも大きい。

メンバーの中で、わりと初期から前向きになっていたのがNVIDIAとMicrosemi、WDといった独自のASICを製造する企業(これらの企業は自社製品の組み込み用にRISC-Vを利用するつもりだった)と、そのASIC向けのプロセッサーコアを提供するメーカーだった。

一番最初にRISC-Vが目指した市場は、ASICの組み込み用だった。下の画像はこれを端的に示したものだが、例えばNVIDIAのTegra SoCではCPUコアはCortex-A9で、これにNVIDIAのGPUコアを組み合わせたものである。ただそれ以外に多数の機能ブロックが存在する。

Tegraの場合でもISPやWi-Fiなどの無線系、オーディオ、セキュリティー、パワーマネジメント、画面出力など多数のブロックが存在するわけだが、だいたいにおいてこういう機能ブロックには「1つ以上の」プロセッサーコアが搭載されている。

上の画像で言えば、NANDのコントローラーには、NANDのアクセスやエラー訂正/ブロック代替処理、ランダムアクセスをブロックアクセスに変換などさまざまな機能が要求される。もう少し後の時代になると、このあたりを全部フラッシュメモリー側でハンドリングするUFSストレージが出てくることで処理が楽になるが、この当時はまだUFSが存在しておらず、SoC側で全部ハンドリングする必要があった。

当然このフラッシュの制御のためには、相応の性能のCPUが必要である。ここをケチると処理が間に合わないから、フラッシュのアクセス速度が全体的に低下することになる。これは他のブロックも全部同じことであって、機能ブロックのCPUには次の特徴がある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ