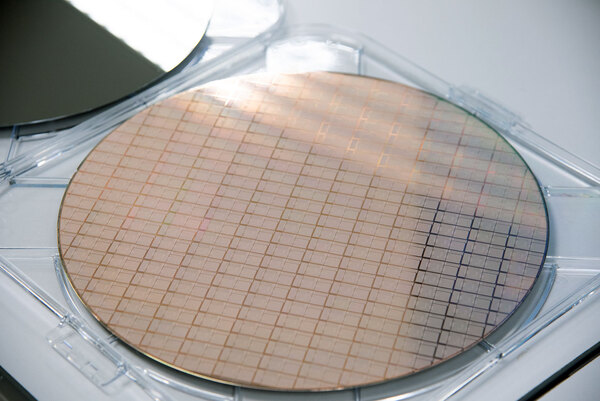

1枚のウェハーから取れるタイルの数は730個弱

ではMeteor Lake関連の話である。ここからは工場見学ツアーの後で、Pat Stover氏(Senior Director, Technology Development)とWilliam Grimm氏(VP, Director of Product Engineering for Logic Technology & Developmen)への質疑応答の機会があり、その中で判明したことが中心である。

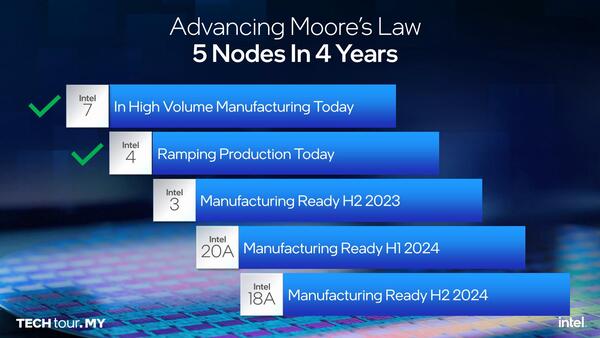

そもそものきっかけは、“5 Nodes In 4 Years”というおなじみのプレゼンテーションについて、「その“Ramping”の厳密な定義はなんなんだ」とGrimm氏に食い下がったのがきっかけである。Grimm氏の返答をまとめたのが以下になる。

- 現在Intel 4の量産はオレゴンのD1でのみ行なわれている。これはD1C/D1D/D1Xのすべてを含んでおり、トータルで月に4万枚が製造されている。ただしこれはすべてのプロセスノードの合計であり、Intel 4だけで4万枚というわけではない。

- アイルランドのFab 34は最初のIntel 4の量産工場であるが、現在はテストチップを流している状態であり、まだ量産には至っていない。

- 今年はIntel 3の製造にも入ることが公言されているが、このIntel 4はIntel 3の改良版といった扱いになる。ただそれ以外に、例えばIntel 7+(Raptor Lakeで採用されたIntel 7のマイナーバージョンアップ版)にあたるようなもの(Intel 4+とでもいうべきか?)があるか? というと、そういう物は予定していない。

- Intel 4でペリクルを使っているかどうかは答えられない。

この最後の答えには少し補足が必要だろう。EUV(極端紫外線)プロセスの仕組みは連載781回で説明したが、光学系の保護(冷却)とゴミの排除のために水素ガスを使っている。ただマスクの保護にはもう1つ、ペリクル(保護膜)と呼ばれるものがある。要するにマスクにEUVを直接当てると、あっという間に劣化してしまう。

そこで簡単に劣化しないように、マスクの表面に保護膜を被せるというアイディアが生まれた。これがペリクルというもので、国内では三井化学がASMLからライセンスを受けてEUV用のペリクルを出荷している。問題はこのペリクルを使うと、どうしても出力が落ちることだ。

もともとEUVがなかなか普及しなかった理由の1つは、EUV生成の効率が悪い(1MW近い消費電力でありながら、EUV出力は200W+αである)ために露光に時間がかかり、スループット(単位時間あたりに処理できるウェハーの枚数)がArF+液浸に遠く及ばないのが挙げられるわけだが、ペリクルを使う場合には、わずかとはいえこれが入ることでEUVの出力が落ちる(ペリクルで反射されたり吸収される)ため、スループットを下げる要因となる。

またペリクルを使うことで余分なコスト増加につながる(もっともペリクルを使うことでマスクの寿命が延びれば、トータルとして低コストになる可能性はあるが)。そんなこともあって、使わずに済むなら使いたくないのがペリクルである。

現時点で言うと、TSMCはペリクルなしでのEUV露光を成功させており、一方Samsungはペリクルありである。インテルは初期にペリクルを使っていたことは周知の事実だが、Intel 4はどうか? というのは不明であり、今回もお答えをいただけなかった。

もっともペリクルなしは技術的難易度が高いので、これに成功していればアピールしてもおかしくなく、その意味では引き続きペリクルを使っている可能性は高そうだが。

ちなみに現時点ではそのIntel 4の歩留まりがどの程度なのかは不明である。D1でどれだけの量のIntel 4が量産できているのかがわからないが、そもそもD1はすべてプロセス開発用の工場で、これを使って無理やり量産している格好だし、そういう状況だから4nmの量産に割けるラインはせいぜい1つだろう。月産4000枚すら怪しく、およそ1000枚程度であろう。D1はIntel 3やIntel 20A/18Aの開発も担っているので、すべてのEUV露光機をIntel 4の量産にまわすわけにはいかないからだ。

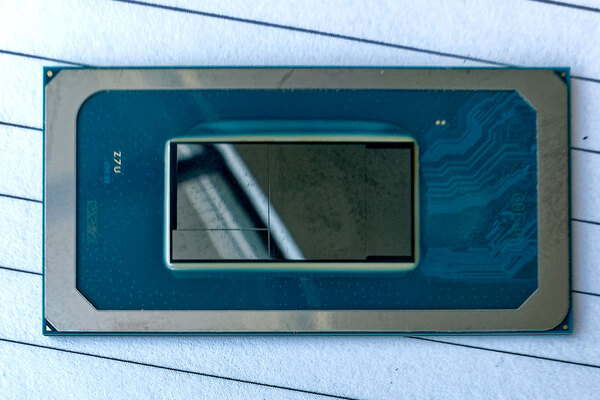

ただ実はこれでもわりと十分である。Meteor Lakeが複数のタイルから構成されるという話は連載682回で説明したが、実際の製品もそんな感じになっている。

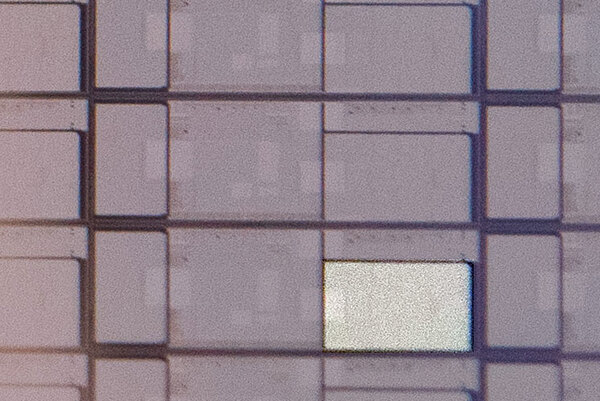

全体ではけっこう大きなMeteor Lakeだが、この中でIntel 4で製造するのは左上のCPUタイルのみである。では寸法はどの程度か? という話だが、インテルがマレーシアツアーに合わせて公開した写真から、長辺方向が300mmウェハーで13個分、短辺方向が26個分と判断できる。つまりMeteor Lakeのタイル全体(ベースタイル)の寸法は23.1×11.5mmと推定される。

下の画像は上の画像を拡大したものだが、CPUタイルの寸法は8.9×8.3mmほどで、73.9mm2程度と推定される。ここまで小さいと、1枚のウェハーから取れるタイルの数は理論的には730個弱まで増える。

こうなると、例えば歩留まりが50%だとしても365個のチップは生き残るし、それが月産1000枚だとしても36万5000個のCPUタイルを確保できる計算だ。GPUタイルはTSMC N5、IOタイルとSoCタイルはTSMC N6だし、いずれも寸法は小さいので月産36万個分の製造は容易だろう。

ベースタイルは265.6mm2とやや大きめだが、こちらは22FFLをベースにしたものなのでやはり歩留まりは高い(そもそもここはFoverosのインターコネクトと電力供給用のキャパシターだけなので、製造は全然難しくない)。

月産30万個強、というのはデスクトップ向けには厳しいだろうがモバイルの特定SKU向けには十分であり、なんならもう少し歩留まりや量産枚数が少なくて、月産10万個くらいであっても「量産した」という実績にすることはできるだろう。

とはいえ、これをもって「Intel 4が完璧」と言うにはやや厳しいものがある。まだ具体的な歩留まりや量産枚数が出てきていないし、なによりFab 34が稼働していないのはまだ不安材料である。

さて今回はこのあたりまで。Meteor Lakeの中身などは一切不明なままであり、こちらの詳細は次回のHot Chipsをお待ちいただきたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ