前回に引き続き、2023 Symposium on VLSI Technology and Circuitの内容をお伝えする。

Samsungはロジック回路周りだけでもSF3プロセスの詳細(*1)とSF4Xプロセスの詳細(*2)や、BS-PDNの実装(*3)、そのBS-PDNに利用されるViaに関する分析(*4)と4件もの発表を行なっている。今回はそのうち、冒頭のSF3プロセスの詳細について説明しよう。

(*1) T1-2:World's First GAA 3nm Foundry Platform Technology (SF3) with Novel Multi-Bridge-Channel-FET (MBCFET) Process

(*2) T16-3:Highly Reliable/Manufacturable 4nm FinFET Platform Technology (SF4X) for HPC Application with Dual-CPP/HP-HD Standard Cells

(*3) T4-1:Breakthrough Design Technology Co-Optimization Using BSPDN and Standard Cell Variants for Maximizing Block Level PPA

(*4) TFS2-5:Structural Reliability and Performance Analysis of Backside PDN

Samsungのロードマップ推移

そもそもSamsungのプロセスロードマップを取り上げるのがひさびさ(前回は2017年の連載418回だった)ので、アップデートも兼ねてまずロードマップ全般について。

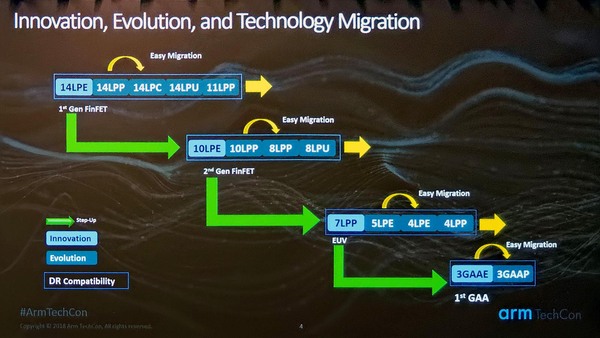

2017年の時には14nmに加え、10nm(10LPE/10LPP)を量産開始し、その微細化版である8LPPを追加。一方最初のEUVを利用した7nmの7LPPの後に、6LPPを追加するというあたりまでを説明した。

そのSamsungの2018年におけるロードマップが下の画像だ。2017年には、4nm世代でGAAを導入するという話だったのが、一世代ずれて3nm世代に移行。4nm世代は5nm世代の改良版のFinFETプロセスのままという形になった。

この当時の説明は「4nmはGAA(Gate All Around)を使わなくても実現できる目途が立った」とのことだったが、要するにまだこの当時はGAAの技術的難易度が高かったので1年先送りした、という形だろう。2018年10月に開催されたArm TechConの際に開示されたロードマップは下の画像のようになっていた。

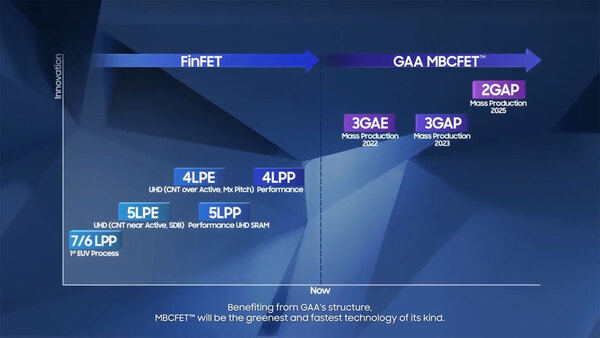

これが2019年になるとどう変わったか? というのが下の画像である。7LPPからすぐに5LPEに移るのではなく、6LPPが追加になった。また4LPPがラインナップから消えている。逆に3nmに関しては特に変更はない。

2020年はCovid-19の影響などもあってSFF(Samsung Foundry Forum)が開催されず、そのため特にロードマップの開示もないが、この2020年は大きな変更はなく、4LPEをやるかどうか怪しいといった話が漏れ伝わってきた程度だ。

このロードマップが更新されたのは2021年である。SFFがオンラインで開催され、ここでいくつか更新があった。最大のものは4LPPが復活したことと、3GAPの後に2GAPが明示されたことだろう。

そして2022年であるが、6月末に3GAEプロセスの量産開始が公式に発表された。もっともこれは、当初は歩留まりが10%台というすさまじい数字だったらしいが、その後の改良も目覚ましく年末には40%まで達したらしい。

いや40%で満足してしまってはまずい気もしなくはないのだが、もともと3GAEは“3nm GAA Early”という、いわばGAAの評価用とでもいうべき最初のプロセスで、顧客の量産は次の3GAP(3nm GAA Performance)で手掛ける予定になっていたので、これは大きな問題ではないともいえる。

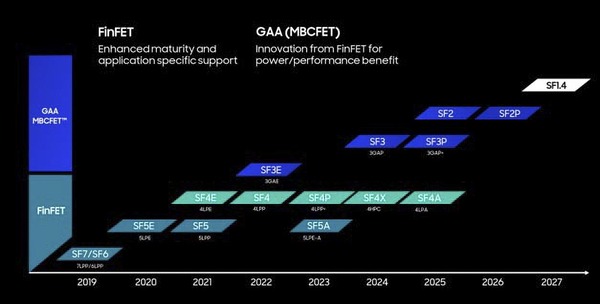

その2022年の10月にSFF 2022が開催されたが、ここで示された新しいロードマップが下の画像だ。名称が従来のものからSFxxに切り替わったのは、TSMCのプロセスなどと混乱しないように、頭にSamsung Foundryの頭文字としてSFを追加したということのようだ。

そしてプロセスであるが、まず旧3GAPであるSF3が2024年提供開始と1年後送りになり、また2025年にはSF3PというSF3/3GAPの改良版が投入されることが明示された。同じ2025年に旧2GAPがSF2として投入され、2026年にはその改良型であるSF2Pが投入されること、そして2027年には1.4nmプロセスに相当するSF1.4が投入されると明示されたことだ。

このSF3P/SP2Pの存在の公開と、2027年にSF1.4を投入という時期の公開が初めて行なわれた形になる。

ということで駆け足でここ数年のSamsungの先端ロジックのロードマップ変遷を解説し終わったところで、SF3の話に移りたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ