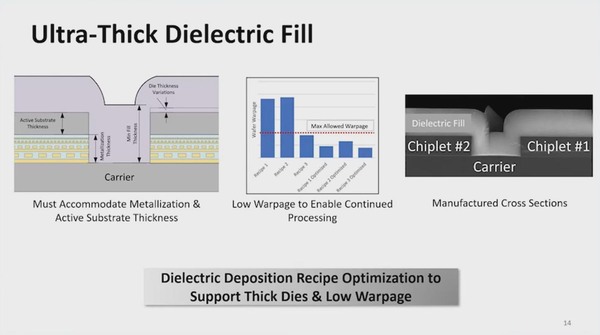

Hybrid Bondingは土台の反りをいかに抑えるかがポイント

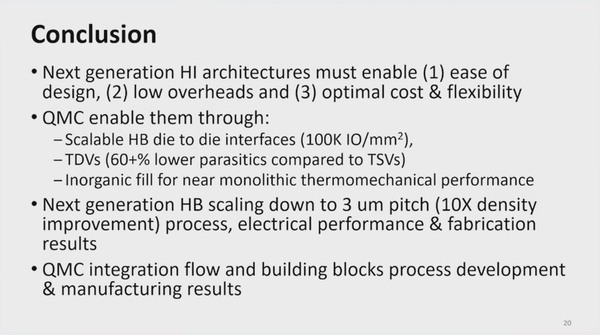

下の画像が今回試作されたHBの断面写真となる。一見する限りはかなり綺麗に接続できており、またテストの結果も良好とのこと。

微妙にChipletのずれはあるが、問題なく接続できていることはわかる。ただ接続部の幅が1.5μm程度しかないので、Chiplet同士のずれを0.1μm未満に抑えないと厳しいわけで、より精密な制御が必要になる

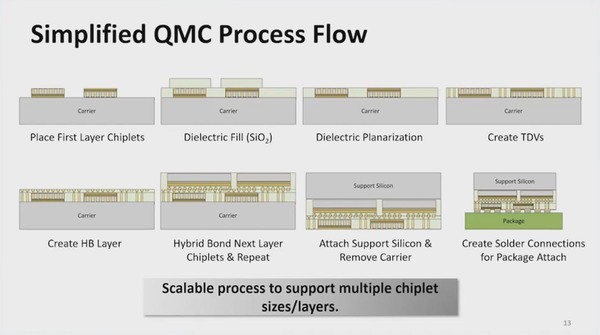

下の画像がこのHBを構築するための製造プロセスである。

左上から横方向に順に、下のようなけっこう面倒な処理になっている。

- 1:土台(Carrier)にChipletを置く

- 2:その上に誘電材を構成する

- 3:CMPを使ってこれを平坦化する

- 4:必要な個所にTDVを構築する

- 5:全体の上にHB層を構築する

- 6:1~5をもう一度繰り返し、製造されたTop Chipletをひっくり返して載せる

- 7:土台を外す

- 8:全体をパッケージに載せる

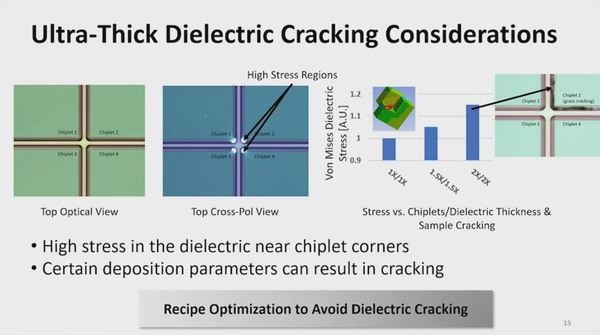

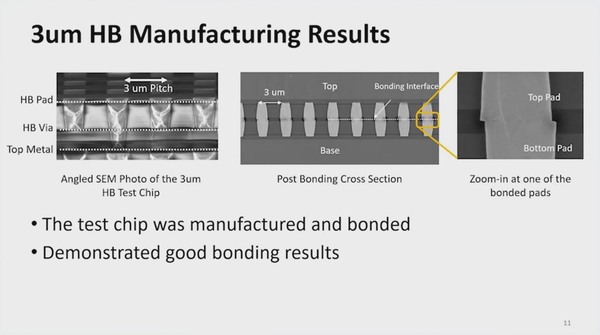

この2番目、つまりChiplet全体を覆うように誘電材を構築するという処理が意外に大変で、土台の反りをいかに抑えるかがポイントとの話であった。

CMPを使うためには通常のシリコンウェハーと同じサイズのキャリアを使う必要があり、当然反りが問題になりやすい。特に左図のように、Chipletの隙間は落ち込むわけで、ここで十分な高さまで誘電材を埋めるのが、反りがあると大変だった模様

またこの角にあたる部分は強度的にストレスがかかりやすいので、欠けないようにするのが大変だったという話も紹介された。

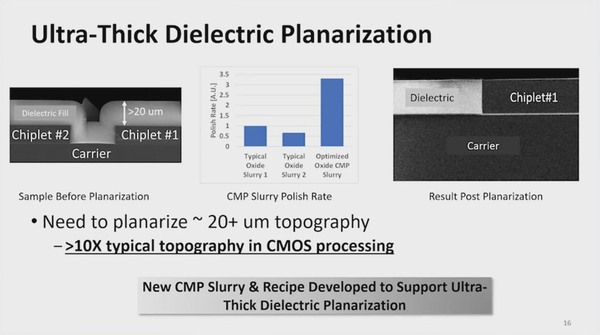

さらに言えばこの誘電材の構築後の平滑化(先の3)にあたっては、20μmほど削り込む必要があるとされる。これは通常のCMOSプロセスの10倍だそうで、通常のCMOSプロセスと同じスラリー(研磨剤)を使っていたら時間がかかりすぎてしまう。

そこでおそらくはもう少し荒い研磨剤を用意するとともに、削り方を工夫することで実現した、とされる。

その分荒れ具合は少し大きくなっているようで、通常のCMOSプロセスで使うスラリーだと0.75~1Å程度を削れるのに対し、今回使ったスラリーでは3.2~3.3Å程度を一気に削れるようになったそうだ。

もちろんこのままでは荒すぎる気がするので、あるいはまずこの荒いスラリーで大雑把に削った後、最後により目の細かい(?)スラリーでより厳密に削ったのかもしれないが(どの程度まで削れば分子間力での接続に十分なのか、に関して筆者は情報を持っていない)。

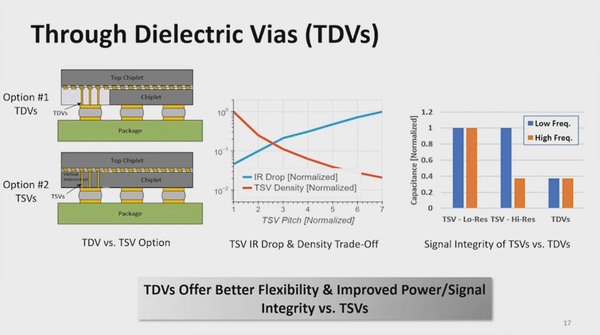

ところで先にTDVについて少しだけ触れた。一般にはこれはTSV(Through Silicon Vias:シリコン貫通電極)を使うが、インテルはこれをTSVではなくTDVを使うのが効果的としている。両者の違いは材質で、要するに銅配線を使うか、誘電材を使うかである。

CMOSプロセスではここにタングステンを使ったりするが、TSVでは通常銅である。ではTSVをTDVにするとなにが良いか? というのが下の画像だ。

TSVは配線密度を上げると配線抵抗も急速に増えることでIR Drop(要するに電圧降下だ)も大きくなる。一番右のグラフがわかりやすいが、TSVでは配線に起因する寄生容量が比較的大きく、また信号周波数の影響を受けやすい。TDVだとこの影響が少ないため、Power/Signal Integrity(電源供給や信号送受信の収束性)が向上する、とのことだった。

今回の発表は、「次世代の」Foveros Directを目指したものであり、3μmまで配線ピッチを縮めることが現実的に可能、というものとなっている。こうなると1mm2あたり11万1千本以上の配線密度を実現可能で、しかもTSVを利用した場合より良い伝達特性が実現できる、というものであった。

少なくとも2023年後半登場の第1世代Foveros Directには利用されないので、今すぐどうこうという話ではないが、まだまだ3Dパッケージング技術は発展の余地がある、ということを知らしめる発表となった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ