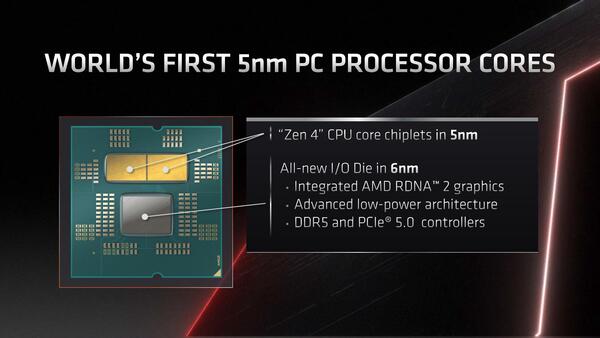

パッケージとチップレット

今回、ヒートスプレッダを外した状態でのCGが示されたが、こちらは筆者の予想から大きく外れたものになった。予想というのは連載652回でしたものだ。

そもそもヒートスプレッダがパスコンを逃がすようにあちこちに空隙のあるユニークな形で、ということは相当パスコンをパッケージの外側に追いやっていると考えられるので、あるいは中央にCPUダイを5つ搭載できるのではないか? という推定であるが、これが見事に外れた格好になる。

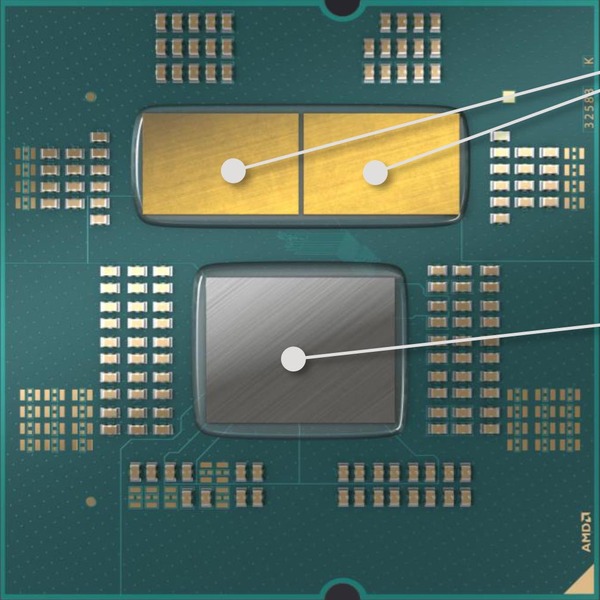

というよりも、予想以上にCPUダイが大きかった。下の画像は元のスライドから原寸大でパッケージを切り出したものだ。

パッケージは相変わらず正方形で、見た感じではSocket AM4から大きく寸法そのものは変わっていないように思われる。ただパッケージサイズが同じでもPGAからLGAに代えるだけでピン数は増やせるので、同じでも問題はないはずである

このパッケージサイズがAM4と同じ40×40mmと仮定すると、それぞれのダイサイズは以下のようになる。

CPUダイ:10.4×6.7mm=69.7mm2

I/Oダイ:12.6×9.7mm=122.2mm2

AMDの公表したCGが正確である、という但し書き付きではあるが、±0.1mm程度の精度で正確な数字である。筆者はZen 4世代をCPUダイが40mm2程度と推定していたが、これがまるっきり外れた格好だ。予想以上にZen 4のダイは大きい。69.8mm2というのは、ほぼZen 3のダイと変わらない大きさである。

I/OダイがN6に移行したにも関わらず引き続き122.2mm2と大きいのは、ここにRDNA2コアを搭載していると考えれば納得が行くのだが、このCPUダイの巨大化は想像できなかった。

逆になぜこんなに巨大化したか? が次の疑問である。TSMCはN7からN5でエリアサイズを45%縮小したとしている。それにもかかわらずダイサイズがほぼ変わらないというのは、つまりCPUダイに搭載されるトランジスタ数が45%増えたということである。

1つ明確にされているのは、2次キャッシュの容量をZen 3の512KBから1MBに倍増したことであるが、これで大きくダイサイズが増えるか? といったらそんなことはない。せいぜいが2~3%といったところだろう。

AVX-512の実装も、実はそれほど難しくない。なにしろZen 3でも256bitのAVX2命令を2命令/サイクルで実装できるFPUが搭載されているわけで、これを2つ連動させれば512bitのAVX-512命令を命令/サイクルで実行で きる計算になる。

もちろん若干の手直しと、レジスターの拡張は必要である。現状Zen 3の拡張レジスターはSSEの128bitとAVX2の256bitにしか対応していないので、これをAVX-512の512bit幅に広げる必要がある。ただこれをやっても、ダイサイズへの影響はやはり1~2%ほどになるだろう。

ではいったい何が? というのは、実をいうと現時点では筆者も解を持ち合わせていない。このダイサイズはまったくつじつまが合わないのだ。

ついでに言うと、後述する理由で連載652回で説明した「Zen 4では5命令デコード/10命令発行のパイプライン」という推定がちょっと怪しくなっている。ひょっとするとZen 4のパイプラインはZen 3と大きく規模は変わらず、単にAVX-512周りにあわせてFPU側のみが手直しされただけ、という可能性もある。

AMDとしても、プロセスの変更とアーキテクチャーの大幅改良を同時にやりたくなかった、という可能性がある。ただそうなると、ますますダイサイズがこんなに大きくなる理由がわからないのである。このあたりは今後もう少しAMDが情報を出してくれるまでの筆者の宿題としたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ