PowerViaが解決すべき問題点

こうしてみるとPowerViaは確かに優れているのだが、その一方で以下のような問題もある。

そもそも電源ラインに関しては、ベースとなるSiliconを貫通する形で電極を形成する必要がある。また厚みも当然薄くしないといけない。

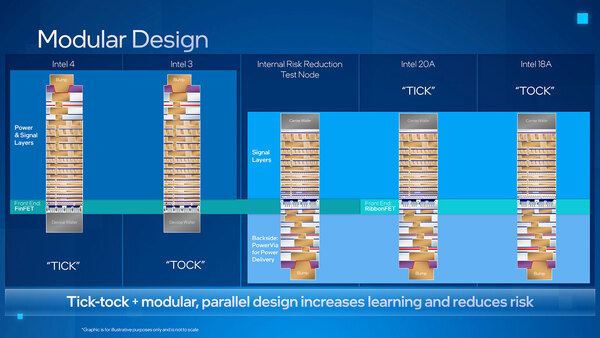

結果、作り方がまったく変わることになる。従来はシリコンウェハー(デバイスウェハー)の上にまずフロントエンドの回路を構築し、その上に配線層を構築する形だったが、PowerViaではまずシリコンウェハー(キャリアウェハー)の上に信号配線層を積層、ついでフロントエンドを積層し、最後に電源配線層を積層することになり、これまでとは異なった製造方法が必要になる。

従来は、外部への信号はパッケージの一番上(上の画像の左側で言えば、一番上の“Bump”という箇所)を経由して接続されていた。Flip Chip Packageというのは、つまり上の画像の構成を上下逆にしてパッケージに載せるという格好であった。ところがPowerViaの場合、ダイの上下両方にBumpが来ることになる。

上の画像の右側で一番上(Carrier Wafer)にはBumpが形成されていないが、もし外部の信号を底面(電源部のBump)に引き回すとしたら、つまり信号配線層から電源配線層まで貫通する配線が別途必要になる。これをどう解決するつもりなのか、まだ見えない。

従来は、一番発熱が多いフロントエンドの真裏にシリコンウェハー(デバイスウェハー)があり、デバイスウェハーを経由して放熱が容易だった(だからこそ、ダイを削って放熱を改善するという恐ろしい技が可能だった)。

ところが今回フロントエンドはダイのちょうど中央に位置することになり、放熱の効率が悪化する可能性がある。普通に考えれば電源配線のメタル層を使って放熱することになると思うが、だとすると上の画像の底面のBumpとヒートスプレッダが(薄い絶縁材を挟んで)接触する位の配慮が必要になるが、それが可能かどうかわからない。

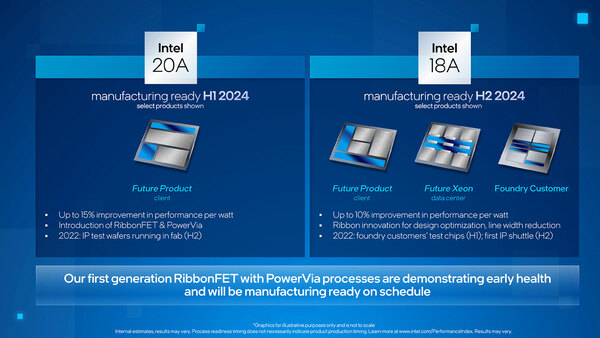

このあたりの問題点をIntel 20Aが量産に入るまでにどう解決するつもりなのか、楽しみである。

Intel 4とIntel 20Aはインテル社内専用のプロセス

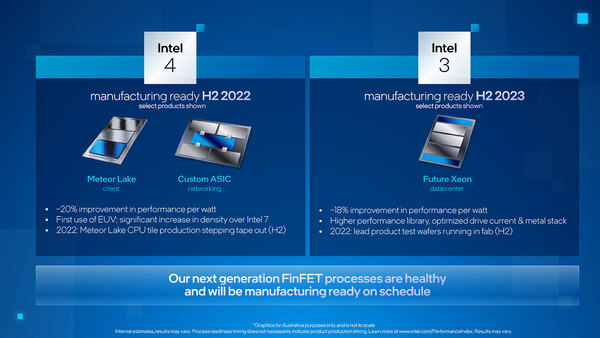

さてそれはそれとして、プロセスの割り当てがおもしろい。現在の予定では、Intel 4はMeteor Lakeとネットワーク向け製品に、Intel 3は将来のXeonにそれぞれ利用するとし、Intel 20AはMeteor Lakeのみ。Intel 18AではLunar LakeやGranite Lake(あえるいはその次)を量産するというロードマップが立てられている。

2023年後半ということで言えば、時期的にはEmerald Rapidsになりそうな感じではあるが、量産開始≠出荷開始という現状を考えると、Emerald RapidsはTSMCで、次のGranite Rapidsという可能性もある

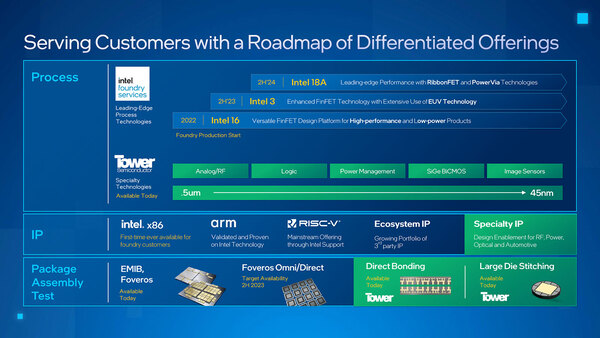

どうもIntel 4、それとIntel 20Aは「実験的ノード」という扱いに近いようで、そもそもファウンダリー・サービスのメニューに入っていない。ではそのファウンダリー・サービスのロードマップは? というのが下の画像だ。

のっけからIntel 16という初耳のプロセスが登場しているが、これは14nm(14nm+なのか14nm++なのか14nm+++なのかは不明)をベースにした車載向けのプロセスである。いわば既存プロセスの再利用という扱いだ。これに加え、Intel 3が2023年後半に、Intel 18Aが2024年後半に予定されている。つまりIntel 4とIntel 20Aはインテル社内専用のプロセスとなるわけだ。

ただそのわりには採用製品がそれほど多くない(少なくともXeonとIntel Arcの採用が現時点で明言されていない)というのは、この2つのプロセスはある程度困難なことが予想されており、ここでトラブルの洗い出しを済ませたうえで改良されたIntel 3/Intel 18AをXeonやファウンダリー・サービスで提供するのかもしれない。

意外に(というのも失礼だが)堅実な策を取ったという気もするのだが、かつての14nm(初代)や10nm(初代)のように、修正に1年以上かかったりしないと良いのだが、と思わざるを得ない。

※お詫びと訂正:写真に対する説明に誤記がありました。記事を訂正してお詫びします。(2022年6月4日)

IDM 2.0は新世代のプロセスが出ても

引き続き旧世代のプロセスを生産していく仕組み

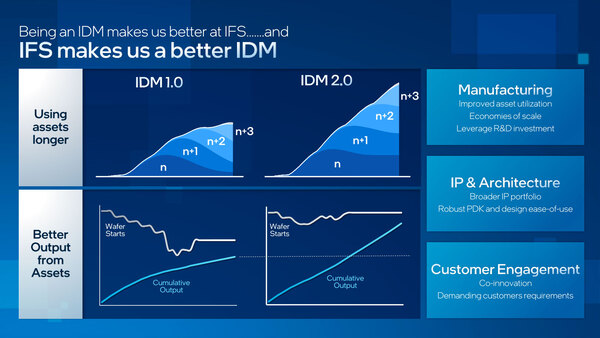

ところでGelsinger CEOは就任直後からIDM 2.0を標榜したわりには、なにが2.0なのかがさっぱりわからなかったのだが、今回もう少し明確な定義が出てきた。

従来では、例えば22nmプロセスが利用可能になった時点で32nmプロセスを使ったCPU製造はフェードアウトしていった。もちろんその後はチップセットの製造に使われたが、出荷量そのものは減っており、ついで14nmプロセスが実用になった時点でチップセットも22nmに移行し、32nmを使う製品はごくわずかになった。

そんな感じで、せいぜいが最新プロセス+2世代程度しか利用されないのがこれまでのインテルのやり方、言い換えればIDM 1.0だった。もちろん一部組み込み向けなどで長期供給に向けて完全にラインを撤廃はしないものの、そうした古いプロセスに関しては一ヵ所に集約し、残りのファブは最新プロセスに転換するという形でファブの再利用を行なっていたわけだ。

ところがIDM 2.0では、今後新世代のプロセスが出ても、引き続き旧世代のプロセスが継続して生産されることになる。ファウンダリー・サービスの顧客は必ずしも最新プロセスが必要とは限らないので、そうした顧客を多く獲得することで、長期にわたって古いプロセスを提供し続けるという戦略だ。

一般論として、ファブは運用を開始して3年~長くても5年程度で設備投資を償却し終わる。すると、後は製造に利用する資材の原価だけで製造できるので、財務上も非常に美味しいことになる(もっともこれも10年や20年を超えると、今度は製造設備がぼちぼち壊れ始めるので、永遠に続くわけではない)。なので、いかにそうしたプロセスを魅力的にして、顧客に長く使ってもらえるかがIDM 2.0の鍵になる。このあたりの損得勘定は、製品ラインナップの話とも絡んでくるので、次回もう少し説明しよう。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ