コア数を増やすトレンドに従い

Zen 4 Ryzenには4ダイ構成が投入される?

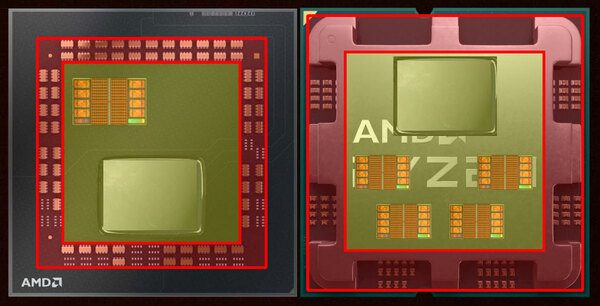

次に、明らかに余分なスペースが増えたZen 4 Ryzenの目的は何か? という話だが、筆者なりの回答が下の画像だ。つまり4ダイ構成で最大32コア/64スレッド製品がZen 4世代で投入されると予測する。

ここではCCD/IODともにZen 3のものを等倍拡大したが、実際にはIODはもう少し横長になるかもしれないし、CCDの縦横比が変わっても不思議ではない。配置もこんな風にならずに、もう少し整然と並ぶ可能性もある。あくまでもCCD×4+IODになる、という以上の意味ではない

これはパッケージサイズからの推定ではあるが、市場の需要を考えても理にかなっている。まずZen 4の世代ではGenoaが96コア/192スレッドになり、Bergamoは128コア/256スレッドに達する。

ということは、Threadripper Proも当然ハイエンドは96コアであり、ミドルレンジが72コアや48コアになる。つまり32コア製品は、Threadripper Proで出るかどうか微妙なラインになるわけだ。

加えて、インテルもこの市場に多コア製品を投入する。Alder Lakeは8P+8Eで16コア/24スレッドだが、次のRaptor Lakeは8P+16Eで24コア/32スレッドに達すると言われており、コア数が増えるトレンドそのものは引き続き健在である。

昨今ではAIを利用した機能を搭載したアプリケーション(Photoshopだけでなく、Officeなどにも搭載されている)が増えており、コア数の多さがそのまま性能に直結しやすい環境がそろい始めてきたこともこれを後押ししている。

もちろん全SKUが4ダイというわけではなく、Ryzen 9(あるいはさらにその上?)のSKUだけで、ローエンドは1ダイということになると思うが、製品差別化という観点でもダイ数のオプションが広がるのは悪いことではない。

ちなみに上の画像でIODが上側に配されているのは、パスコンの位置関係からの考察である。IODにもパスコンは必要だが、それよりもCCDの方が消費電力が多いから、当然CCDのそばにパスコンを並べる必要がある。そうなると、下半分にCCDが集まり、上側にIODという位置関係になるかな? というのが筆者の判断だ。

ついでに内部構造についても簡単に触れておきたい。実はいまだにZen 4の正確な中身は不明である。以前Ryzenが出る「前」に、GCCに対するzenver1パッチの情報から内部推定をしたことがある。その後AMDはZen 2/Zen 3に対するGCCパッチを投稿しているのだが、現在進行中のGCC 12に対してのzenver4パッチがまったく上がっていないためだ(Redditでもこの件で投稿があった)。

ただ筆者は別件でZen 3の内部解析をした結果で言えば、4命令同時デコードのx86プロセッサーとして、Zen 3コアは一番高い完成度を持っていると判断している。

もちろん改良の余地があり、それはZen 3+としてリリースされたわけだが、競合であるAlder Lake(Golden Cove)はPeak 6命令/サイクル、Sustained 5命令/サイクルのデコーダーとそれをカバーするアウト・オブ・オーダー構成のバックエンドを組み合わせることでZen 3を上回るIPCを実現しており、AMDもZen 4世代で5命令/サイクルのデコーダー+それに見合うアウト・オブ・オーダーのバックエンドを実装すると想像している。

下図は、Zen 3の構造をそのまま5命令/サイクルに拡張した構成例だが、整数部はおそらくALU×5、AGU×4、BR×2(うち1つはALUと共用)といった構成になる。

FPU側はZen 3と同じだが、2つの256bit FPUが連携してAVX512演算を1命令/サイクルで処理可能になっていると思われる(これをカバーするために、AGUは×4構成を想定している)。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ