前回に引き続き、AMDが開催したオンラインイベント“AMD Accelerated Data Center Premiere”の内容を説明していこう。今回はGenoaとBergamo、ついでにTurinの話も少々していく。

Zen 4アーキテクチャーを採用する

GenoaとBergamo

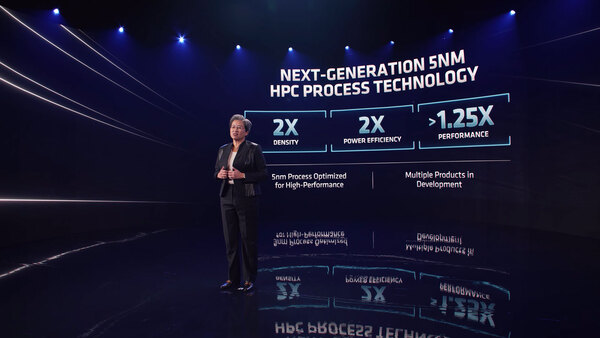

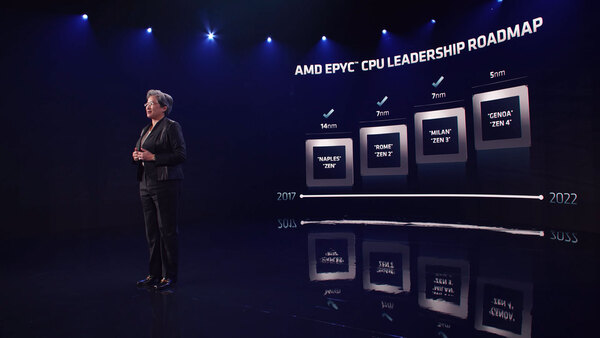

まずは、今後のAMD CPUロードマップの話である。次の世代は以前から説明があったGenoaであるが、こちらは5nmプロセスに移行する。つまりTSMCのN5であるが、これは2倍のトランジスタ密度と2倍の性能/消費電力比、1.25倍の性能を発揮するとされている。

この5nmを利用するのがZen 4アーキテクチャーで、これはGenoaとして以前から名前は上がっていた。そのGenoaであるが、最大96コアで、DDR5とPCIe 5.0/CXLに対応、さらに機能拡張されたセキュリティー機能を搭載するとされ、2022年中に市場投入を予定しているという話だが、すでに顧客にサンプル出荷も開始している、という話が今回正式に語られた。

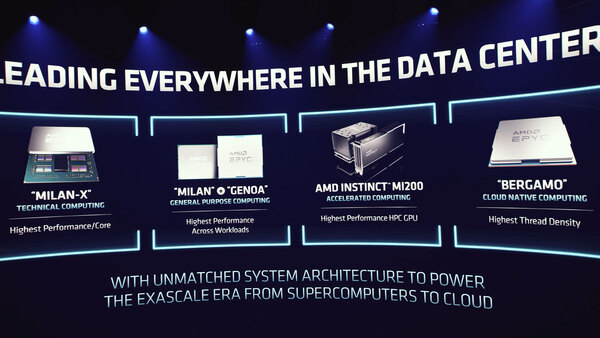

さて問題はこれに加えて発表されたBergamoである。今後のニーズは以下のとおり。

- General Purpose Computing:汎用Computing向け。Milan→Genoa

- Technical Computing:計算主体で大量のメモリーアクセスをするもの。Milan X(これもそのうちGenoa-Xなどがありそう)

- Accelerated Computing:GPGPU向け。Radeon Instinct MI200シリーズ

これらはいいとして、Clound Native、つまりスケールアウト的に利用する高密度サーバー向けのコアが別途必要、というのがAMDの考え方である。

高密度サーバー向けのClound Native Computing。この考え方は例えばArmも同じであり、今年4月に性能はそこそこながらコア数を増やせるNeoverse N2と、コア数は減るがIPCを高めたNeoverse V1という2種類のコアをサーバー向けに発表している

従来AMDやインテルは、これを「有効コア数と動作周波数・消費電力で分ける」という形で対応してきていた。例えばEPYC 7003シリーズで言うなら、ハイ・パフォーマンスを狙う用途はEPYC 75F3のようにコア数を半減させ、TDPも280Wまで引き上げて、その代わりBase 2.95GHz/Max 4GHz動作を可能にする一方、クラウド向けの高密度サーバーにはEPYC 7713のようにコア数を増やしながら動作周波数はBase 2GHz/Max 3.675GHzと低めにすることで、TDPを225Wに抑えるといった具合だ。ただこの方式には以下の欠点がある。

- 高性能向けの場合、コアを無駄に搭載していることになる。本来32コアなら4ダイ構成でもいけるはずだが、それではL3の合計が128MBに減ってしまう。結局8ダイを搭載し、各々のダイのCPUコアを半分無効化して利用しているため、ダイの利用効率が非常に悪い。

- 高密度向けの場合、高速動作可能なパイプラインを無駄に低速に抑えて消費電力を下げることになっている。最初から高速動作を狙わないのであれば、パイプライン構成や物理実装を高効率/高密度向けに切り替えることでさらに効率が上げられるはずで、逆に言えば現在の構成は効率が悪い。

なんのことはなく、Armのbig.LITTLEやインテルのHybrid Architectureと根っこは同じ話である。そこでZen 4をベースに、これを高効率向けに再設計したものがZen 4cとして発表された。

「高効率」の定義が難しいところではあるが、おそらくは動作周波数は低めに抑え、その代わりにコアのエリアサイズを抑えるとともに、消費電力を低めに抑える工夫がなされると思われる。これを論理設計レベルで行なうか、物理設計レベルで行なうのかで話は変わるが、論理設計レベルではけっこう大変な気がする。

ArmのNeoverse V1とNeoverse N2の場合、論理的に異なるコア(*1)になっているが、これは元のコアが2種類あったから可能な話で、同じことをAMDができるかというとやや怪しいように思う。

なので筆者としては、Zen 4はHigh Speed Libraryを、Zen 4cはHigh Density Libraryをそれぞれ利用する形で物理設計を分けており、この結果としてZen 4cはコア数を128まで増やせたと想像している。

(*1) Neoverse V1はCortex-X2ベース、Neoverse N2はCortex-A710ベースと思われ、この2つはそもそもデコードの同時処理命令数のレベルから異なる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ