日本発のベンチャー企業に、ArchiTekという会社がある。創業は2011年であるが、実は創業メンバーはPanasonicのスピンアウト組である。実際役員構成を見ると、CFOを務める藤中達也氏以外は全員がPanasonic出身となっている。代表取締役兼CTOを務める高田周一氏にしても、40代でPanasonicを辞してArchiTekを立ち上げている。

ただArchiTek、これまであまりニュースに上がることはなかった。ASCII.jpの過去記事を探しても、2018年にさくらインターネットと協業した記事が見つかった程度である。ところが今年2月に、やっとbeppuことAiOnIcのサンプルチップが完成したリリースが出たあたりからいろいろと会社アピールを始めたようで、創業者インタビュー記事なども出てくるようになった。

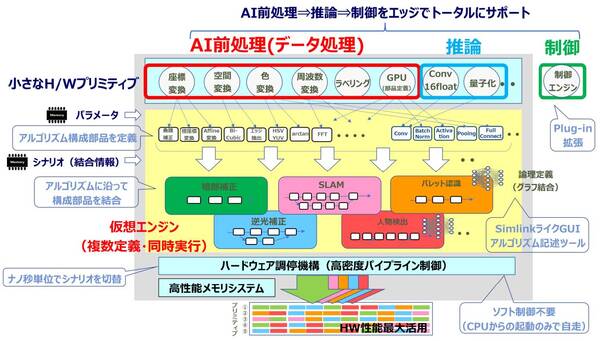

もっとも肝心のAiOnIc(アイオニック、と呼ぶようだ)チップの詳細などは明らかにされておらず、ウェブページから入手できるホワイトペーパーの解説図も、今一つ内部がわからない感じになっている。

ところが今年10月20日から開催されたLinley Fall Processor Conference 2021でこのAiOnICの詳細が明らかになったので、この資料を基に内部を説明したい。

試作チップの「beppu」と量産チップの「chichibu」

まずAiOnICチップの目的である。ArchiTekはエッジAI向けの製品を志向しており、これに向けて低価格・低消費電力で、それでありながらそこそこの性能(2TOPS以上、というのは結構高い目標に思える)を実現することが必要、としている。

もっともここに挙がっている項目は、どんなエッジAIチップでもだいたい目標とするようなものだが、量産コストで10ドル以内というのはベンチャーには厳しい。

とりあえず設計やソフトウェアのコストを考えずに、純粋にウェハー製造コストだけで言えば、TSMCの12nmプロセスの場合はだいたい1枚4000ドルとされる(2020年の推定)。ということは、300mmのウェハーで400個のチップを取れないと、10ドルにはならない計算だ。

実際には歩留まりの問題などもあるため、もう少し多めに450~500個くらいチップを取れないと難しい。300mmウェハーで450個のチップを取ろうとすると、120mm2以下にダイサイズを抑える必要がある。100mm2というのは、MCUを見慣れた目にはかなり大きいダイに見えるが、AI向けに多数の演算器とSRAMを搭載するとなると、相当厳しい数字である。

それに加えて、ベンチャー企業の場合はそんなに多数のウェハーをいきなり発注したりできないから、シャトルサービスを利用しての混載(1枚のウェハーを複数の顧客のチップでシェアする方式。例えば右半分はA社の、左半分はB社の製品のマスクでそれぞれチップを製造し、完成後のダイシングの段階で別々に分ける格好になる)での製造になる公算が高い。

そうなるとどうしても価格が高くなりがちであり、それを前提に10ドルで抑えようとすると、実際のダイサイズはさらに小さな、それこそ80mm2や90mm2に抑えないとかなり厳しい気がする。当然その分回路規模も小さくなるので、性能を上げにくい。しかも2TOPSという絶対性能と2W以下の消費電力を満足させる必要があるわけで、普通に力技で作ったら要求は満たせないだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ