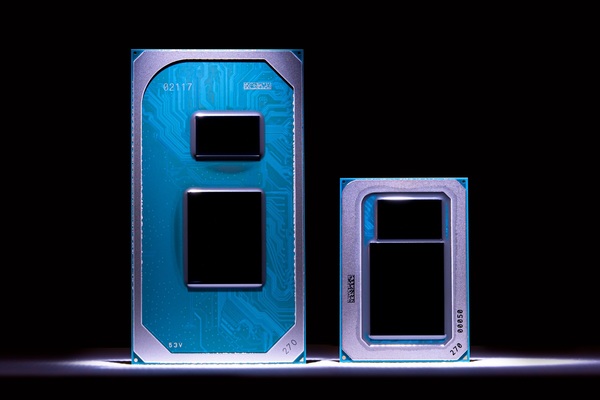

CPUとPCHの統合でダイサイズが肥大化

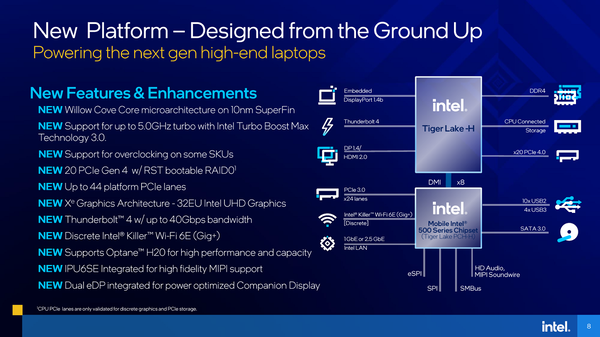

KTU氏による発表記事のスライドにもあるように、少なくとも論理的にはCPU本体とTiger Lake PCH-HというPCHが別々に存在し、間がDMI 3.0×8で接続される構造になっているが、物理的には(Ryzen Gなどと同じように)ワンチップ化したことになる。

ワンチップ化そのものは別に珍しい話ではなく、これまでも例えばGoldmontベースのApollo Lakeなどは1つのダイにCPUとPCHを統合していたので、これが初めてというわけではない。強いて言うなら、PCHに10nmプロセス(それも10nm SuperFin)を使ったのはこれが初めてというあたりだろうか。

PCHのエリアに関してはわりと適当である。3つ前の画像では、ダイ左上に全体の8%程度の面積として入れてあるが、もう少し小さいかもしれない。というのは、上の画像の図にもあるように、Tiger Lake PCH-Hの機能は限られているからだ。

まずIntel Killer Wi-Fi 6Eはディスクリートなので、実際はPCIeの先に拡張カードの形で接続される。またSATA 3.0は一応あるにはあるが、ポート数自体は1か多くても2ポートだろう。

ノート向けであればそもそもSATAポートが多数用意される必要がない。もう最近はDVD-ROMドライブを搭載する機種も激減したし、せいぜいがデータ用にSATA SSDを拡張できるポートがあれば十分というあたり。性能が必要な場合はNVMe SSDを使えばいいからだ。

仮になにか特殊な理由でOEMがどうしても多数のSATAポートが必要というなら、ポートマルチプライヤーを使ってSATAポートを増やすこともできるから、これはOEM側だけで対応できる。となると、PCIeレーンとUSB、1/2.5GbE、HD Audio、SMBus、SPI/eSPIあたりがあればいい。

USB 3までであればすでに実績のあるコントローラーが多数あるし、エリアサイズも小さい。PCIeはさらに簡単で、Root Complex(PCIe全体を制御する部分)はホスト(つまりTiger Lake-Hのアンコア部)に搭載されているから、PCHの側は単にPCIeスイッチが入っているだけである。

その他のI/Fもあまりエリアサイズを喰いそうなものはないので、上で8%ほどのエリアサイズと推定はしたものの、実際には5~6%で収まっている可能性もある。

余談になるが、通常PCHは結構なエリアサイズを喰う。理由はアナログ回路に必要な受動部品(特にコイルとコンデンサー)は微細化と無縁(どうしてもそれなりのサイズが必要)なためだ。ただTiger Lake PCH-Hではこうしたアナログ回路がほとんど搭載されていないようで、そのあたりも統合できた理由かもしれない。

もっともこれは言い方を変えれば、インテルはアナログ部品まわりは鬼門で、これまでもいろいろな不具合を出しまくっているだけに、極力PCHにアナログ回路を含まない方向にシフトしているようで、そうしたことも結果的にPCH統合に貢献しているのはなんというべきか。

これはインテルだけでなくAMDや昨今のARM SoCも同じで、プロセッサー性能を引き上げる&製造コストを引き下げるためにはなるべくチップセットの類を1つのダイに統合する必要があるが、その一方で先端ロジックプロセスは、あまりアナログ統合が得意ではない。

であれば、アナログ部品がどうしても必要なら別チップに切り出す方向で、なるべくデジタル回路(とデジタルI/F)だけでチップセットを完結させる方向にシフトしつつある。その意味でもインテルの方向性は間違ってはいないのだが。

話を戻すと、このPCHを統合したことも、ダイサイズの肥大化に一役買っているのは疑う余地もない。それでもCPU+PCHで2ダイになったTiger Lakeとどちらがコスト的に有利か、は微妙なところである。

訂正:記事公開後にインテルが仕様を公開し、Tiger Lake-HのPCHは統合されておらず、別チップであると判明しました。詳細は連載617回で説明しておりますので、そちらをご参照ください。(2021年5月31日)

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ