今回はTiger Lake-Hについて深堀りした情報をお届けしよう。Tiger Lake-HことCore i9-11980HKやXeon W-11955Mなどが5月11日に発表された、という話はKTU氏の記事にまとまっている通りである。実機がないのは筆者も一緒なので、あくまでも公開情報を基にした深堀りとなる。

Tiger Lake-Hのダイサイズは201.4mm2

Tiger Lakeとの大きな違いはダイが1つになったこと

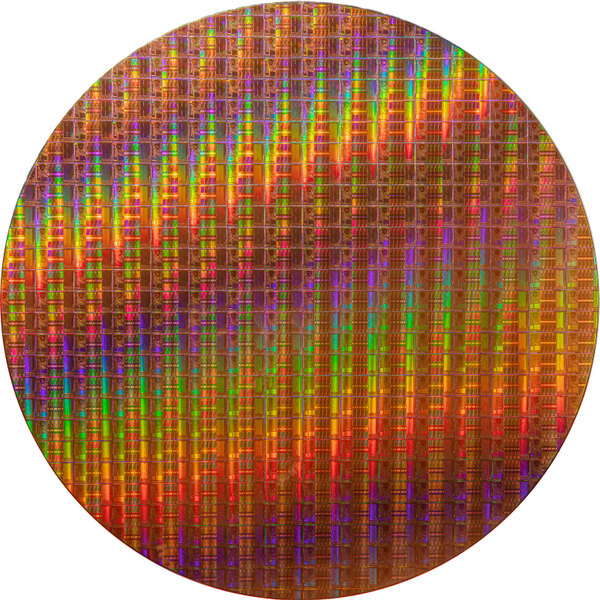

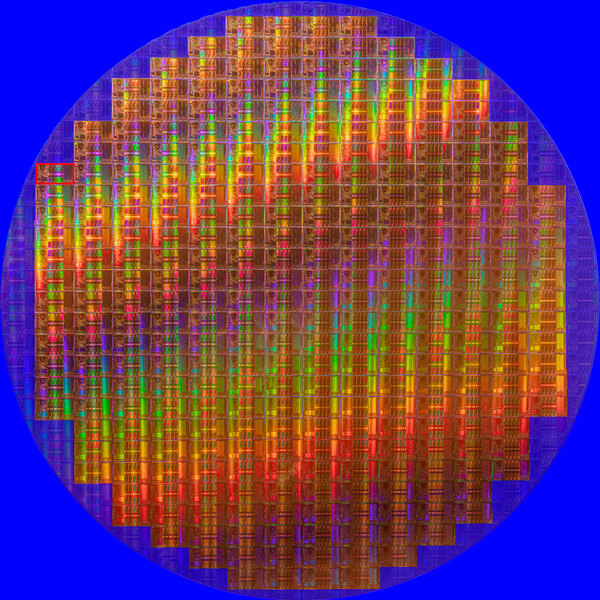

まずはダイサイズについて。下の画像は今回の発表に合わせてインテルから公開された、Tiger Lake-Hのウェハーである。

ここから有効コアのみを抜き出したのが下の画像となる。ごらんのように有効ダイ数は303個に達しており、これはけっこう多そうに見える。

左端の一番上のダイ(赤枠で囲んだところ)はウェハーの縁にギリギリまで接近しており、これが有効かどうか自信がない(Photoshopで拡大してみる限り大丈夫そうに見える)。もしこれが駄目だと、有効ダイ数は302個となる

ただインテルの過去の製品で言えば、Kaby Lakeベースの4コア製品で509個、Coffee Lakeベースの6コア製品で411個、Coffee Lake Refreshベースの8コア製品で344個の有効ダイがあったことを考えると、14nm→10nmで微細化によりトランジスタ密度が上がったとはいえ、それを上回るほどトランジスタの必要数が増えたことで、ダイサイズがやや肥大化したことになる。

ちなみにダイサイズそのものであるが、ウェハーの画像をPhotoshop上でピクセルを数えたところ、縦方向は28.2ダイ分、横方向は15.8ダイ分の寸法となった。ウェハーサイズは300mmなので、1ダイ分の寸法はおおよそ10.6×19.0mmで201.4mm2と算出される。先の例で言えば以下の通り。

| ダイサイズの比較 | ||||||

|---|---|---|---|---|---|---|

| Kaby Lakeベース4コア | 126mm2 | |||||

| Coffee Lakeベース6コア | 152mm2 | |||||

| Coffee Lake Refreshベース8コア | 178mm2 | |||||

Coffee Lake Refreshと比較してもまだ13%ほど大きい計算である。1枚のウェハーから取れる数もやはり13.5%ほど減ってるわけで、つじつまがあっている。したがって、これらの数字は大きく間違っていないと思われる。

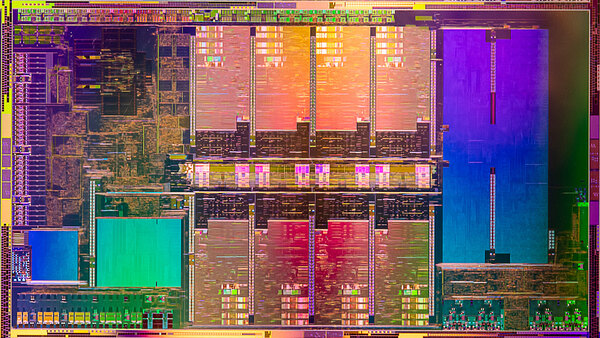

さて、次はなにがこれほど大きくなったか、である。下の画像はやはりインテル提供のダイ画像である。

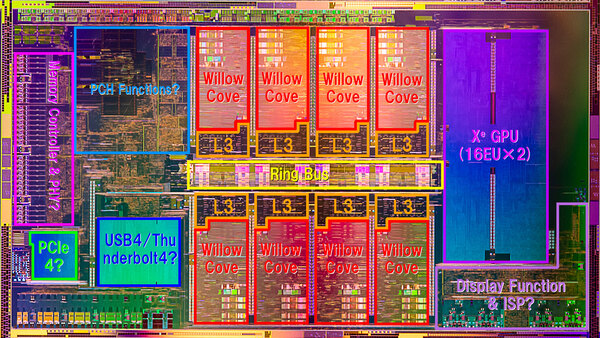

それぞれのブロックの用途を推察してみたのが下の画像となる。中央のWillow Cove×8と3次キャッシュ×8が一番大きな場所を取っているのは見ての通り。ただダイ全体に占める面積で言えば43%程度で、いうほど大きくはない。

そしてその右にあるのがXe GPUとディスプレー関連と思われる出力回路、それにビデオコーデックやISPなどもひょっとしてこのあたりにまとまっているかもしれないが、こちらは全体の26%ほどでしかない(ビデオコーデックやISPはWillow Coveの左側ブロックの可能性もある)。

意外に少ないのはTiger Lake-Hが32EU構成になっているからで、これを96EU構成にした場合、横幅が32%ほど増えて25mmほどになると思われる。ダイサイズで言えば272.5mm2ほどになる計算で、いくらなんでもこれは許容されないだろう。

では残りの31%ほどは? というとWillow Coveの左にあるアンコア部になるのだが、そのアンコア部の下にかなり大きなブロックがデンと控えているのは、おそらくはUSB 4/Thunderbolt 4のコントローラー、それとPCIe 4.0のコントローラーと思われる。

アンコア部の一番下にあるのはPCIeのポート(20レーン分がきっちり見える)、“PCIe4?”のブロックの左にあるのがUSB 4/Thunderbolt 4のポートに見える。

「PCIe4とUSB4/Thunderbolt4のブロックが逆なのでは?」と思われるかもしれないが、Thunderbolt4のコントローラーはけっこうなエリアサイズを喰う(プロトコルハンドリングがいろいろ大変らしい)ことと、USB4もここに含まれることを考えると、こういう並びになるのではないかと考えている。

もう1つ、左端におそらくDDR4/LPDDR4X対応のメモリーコントローラーがあるのは良いとして、その脇にあるブロックは従来のインテルのCoreシリーズに搭載されたアンコア機能だけでなく、PCHがここに入っているものと思われる。

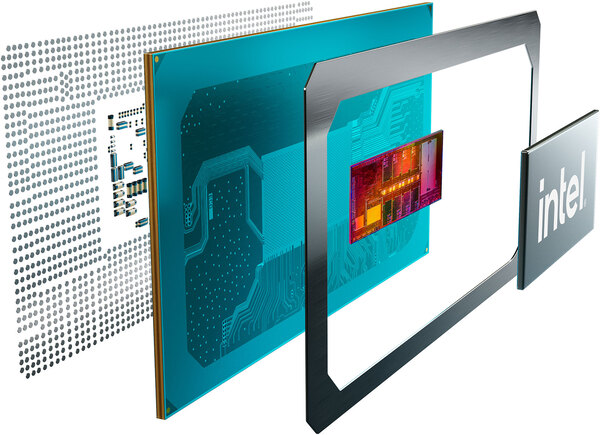

これが従来のTiger Lakeとの大きな差の1つであるが、パッケージの分解写真を見てもダイは1つしかないのがわかる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ