ロードマップでわかる!当世プロセッサー事情 第617回

AMDとNVIDIAがPerlmutterを当初のタイムライン通りに納入 スーパーコンピューターの系譜

2021年05月31日 12時00分更新

インテル CPUロードマップ アップデート

Tiger Lake-HのPCHはCPU統合ではなく別チップ

まず冒頭からお詫びと訂正である。この記事の前半がまるごとお詫びと訂正というべきか。連載615回で筆者はTiger Lake-HをPCHまで統合した構成になっていると説明したが、これが大嘘でしたという話である。

先に言い訳を書いておくと、連載615回の記事公開時には、まだインテルからTiger Lake-Hに対応した仕様が公開されていなかった。一応あの時点で出ていた資料には全部目を通したものの、PCHが物理的にどこにあるかの記述がないため、エイヤで「PCHが統合されたというシナリオ」で原稿を書いたわけだが、その後Tiger Lake-Hに対応した仕様が公開され、やっとここで明示的にPCHが別チップであると判明した次第だ。ということでまずはこのアップデートから。

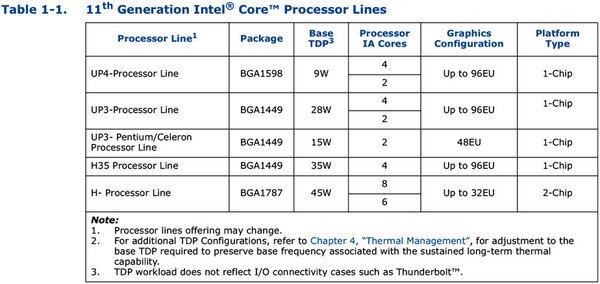

下の画像は先日アップデートされた“11th Generation Intel Core Processor Datasheet, Volume 1 of 2”の冒頭に出てくる表である。

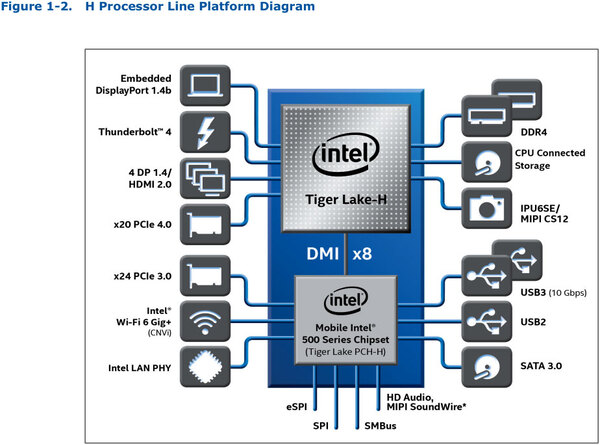

ここではっきり“H-Processor Line”は2チップ構成であることが明示されている。ということは、下図で言うところのTiger Lake PCH-Hは別チップということになる。

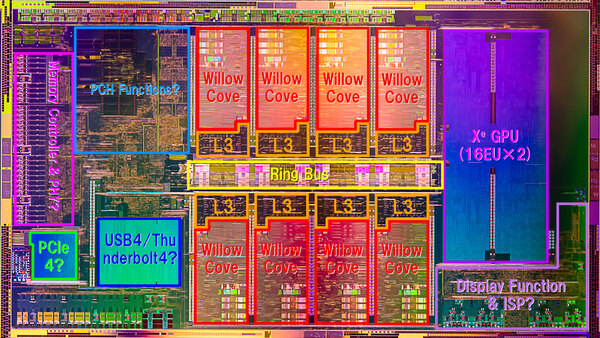

となると次に問題になるのは連載615回で説明したダイの画像だ。左上の“PCH Functions?”のブロックは丸ごとなくなるわけで、ここになにが入るか?という話である。

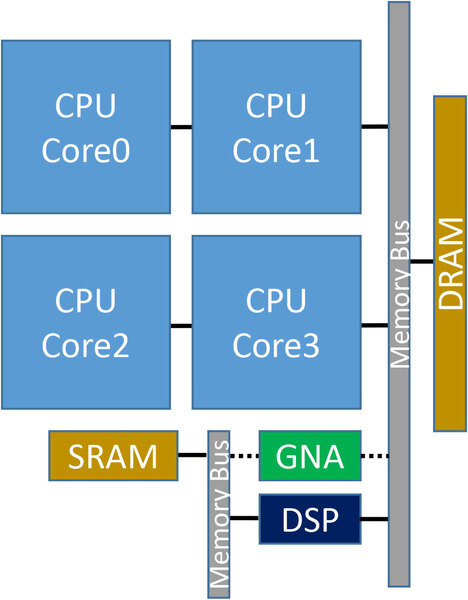

ということで下の画像が修正版となる。PCH Functionがなくなったが、ここになにが入るのか? といろいろ探していて気が付いたのがGNA/DSPブロックである。GNA/DSPブロックはIce Lake世代で搭載されたAI用のアクセラレーターで、以前連載525回で紹介している。前述のダイアグラムを見ても、他に大きな面積を喰いそうなものが見当たらないからだ。

ちなみに“SRAM?”というブロックは、連載525回で説明したGNAとDSP専用のSRAMエリアのことだ。実際にはもう少し縦方向に長い可能性がある(Willow Cove+L3と同じ程度の長さかもしれない)。

話を戻すと、Tiger Lake-Hを使う限りはロジックボード側にPCHの実装が必要になり、連載615回で議論したような低コストのメリットはまったくないという話になる。

この点ではRyzen 3000GシリーズやRyzen 5000Gシリーズに比べて、インテルのTiger Lake系列はまだ一歩およばないという話になった。連載615回でも説明したように、例えばGoldmontベースのApollo LakeではPCHをダイに内蔵しているから不可能ではない。強いて言えば、やはり10nmプロセスではまだ作れないなにかしらの理由があるか、もしくはダイサイズ的に厳しいと判断されたのかのどちらか(もしくは両方)だろう。

もともとLakefieldでもチップセットは引き続き14nmでの製造になっているし、HのつかないTiger LakeでもPCHは別ダイ(Tiger Lake PCH-LP)になっているあたり、まだ10nm世代にチップセットを移行する準備ができていないと見る方が正確なのかもしれない。

ちなみにそのTiger Lake PCH-Hであるが、現時点ではIntel HM570/QM580/WM590という3種類のチップセットが用意されている。こちらはほぼデスクトップ向けのIntel 500シリーズに近いスペックになっている。この3つの違いをまとめたのが下表である。

| 各チップセットの違い | ||||||

|---|---|---|---|---|---|---|

| チップセット | HM570 | QM580 | WM590 | |||

| PCIe 3.0 Lane | x16 | x20 | x24 | |||

| USB 3.2 Gen2x2 | 最大8 | 最大10 | ||||

| USB 3.2 Gen2x1 | 最大8 | 最大10 | ||||

| SATA Port | 4 | 8 | ||||

| vPro | No | Yes | ||||

| SIPP | No | Yes | ||||

| TET | No | Yes | ||||

PCIeはレーン数が16/20/24とそれぞれ4レーンづつ増えていくほか、USB 3.2 Gen2x1/2x2についてはHM570のみ最大8ポート、SATAはWM590のみ8ポート。あとHM570はIntel vProとIntel SIPP(Stable Image Platform Program)、それとIntel TET(Trusted Execution Technology)に未対応という程度で大きな違いではない。

いずれもTDPは3.4W、推奨小売価格は51ドルとなっており、これだけではHM570を選ぶべき理由が今ひとつはっきりしないのだが、あいにくとこのTiger Lake PCH-Hに関してはドキュメントが現時点でも未公開となっており、ark.intel.comの一覧には出てこない違いがまだあるのかどうかはっきりしない。もっともark.intel.comの推奨価格はあくまで一例であって、発注数量が多くなると価格差が出てくる可能性はある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ