ロードマップでわかる!当世プロセッサー事情 第586回

Ice Lake-SPは2021年第1四半期に遅延、Elkhart Lakeの機能追加に仰天 インテル CPUロードマップ

2020年10月26日 12時00分更新

Ice Lake-SPは2021年第1四半期に遅延

ここまでは話の枕であり、本題は10nmプロセス周りである。この10nmプロセスに関しては、アリゾナ州にあるインテルのFab42が10nm(おそらく10nm SuperFin)のフル量産に入っており、1月の時点における予測と比較して30%以上生産量が増えているそうである。

その10nmプロセスを使うIce Lake-SPであるが、決算発表におけるBob Swan CEOによる説明は「現在(Ice Lake-SP)の検証を今年第4四半期中に終わらせることを目標にしており、量産開始は検証終了のすぐ後、2021年第1四半期に開始する」である。

要するに量産を「開始する」のが2021年1月ごろの予定であり、そこから量産を開始し、製品が出てきて出荷できるのは早くて2月だが、これは厳しい。現実問題としては2021年3月になるだろう。Rocket Lakeの出荷時期とそう違わないあたりではないかと筆者は予想している。

ついでにもう1つ。10月21日AcerがIris Xe MAXを搭載したノートを発表したことが話題になった。

これに関してSwan CEOは「われわれは複数のOEMメーカーに対して最初のディスクリートGPUであるDG1を現在出荷中であり、これを搭載した製品は第4四半期の終わりに市場投入されるだろう。これに続き次世代のDG2にフォーカスしている。DG2はやはりXeベースの高性能ゲーミングアーキテクチャーであり、エンスージアスト向けセグメントに投入される予定だ」としている。

さすがに今年中はないと思うが、来年にはハイエンドゲーミングノートでは、例えばGeForce RTX 2000 Max-QとDG2を選べるという時代が来るのかもしれない(Radeon RX 6000も殴り込んできそうだが)。

Sapphire Rapidsの内部構成がリークされるが

情報が不正確とインテルから突っ込まれる

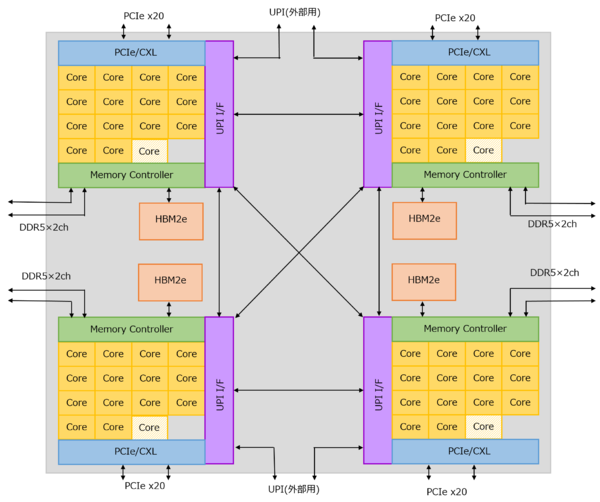

そのIce Lake-SPの後継となるのがSapphire Rapidsになるという話はすでに公開されているが、ADOREDTVがそのSapphire Rapidsの内部構成の概略を報じている……のだが、なんというかいろいろ無茶な構成になっている。

- コアはGolden Coveベース。ダイは60コア分を搭載し、うち56コアを有効化

- 最大80レーンのPCIe Gen5/CXLをサポート

- DDR5-4800メモリーを8ch搭載

- Tile構成。各々のCPU Tileは15コア(うち14コア有効化)

- I/O Tileがあるかどうかは不明

- HBM2eを4スタック搭載、最大64GB(4次キャッシュ?)

- TDPは300~400W

これを図にすると下のようになるのだが、「どこの初代EPYC?」という感じである。

確かにインテルとしては、Xeonのラインナップに向けてHCC/MCC/LCCの3種類のダイを作り分けるのはコストの意味から厳しいとは思うし、すでにPonte Vecchioでマルチタイル構成を実装することは明らかにしているから、これをXeonのラインナップに持ち込んでも不思議ではない。

とはいえ、HBM2eを搭載する(全SKUではなく一部のSKUだけのようだが)のは意味不明だし、PCIeがTileあたり最大20レーンも「ちょっと少なくね?」という気もする。多分に眉唾ものの話であるので、話半分というか話2割くらいに留めておくのが無難だろう。

ちなみにADOREDTVの記事への追記によれば、当初公開したところ「インテルから記事が不正確なので取り下げろ」という通知が来たそうだが、「どのパートが不正確なのか?」と確認したところ返事がなかったそうで、それもあって引き続き記事を掲載しているそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ