ロードマップでわかる!当世プロセッサー事情 第578回

Ice Lake-SPはスループットがSkylake-SPの2倍以上になる インテル CPUロードマップ

2020年08月31日 12時00分更新

Ice Lake SPでは256H/512L系の命令を

動作周波数を下げずに実行可能になった

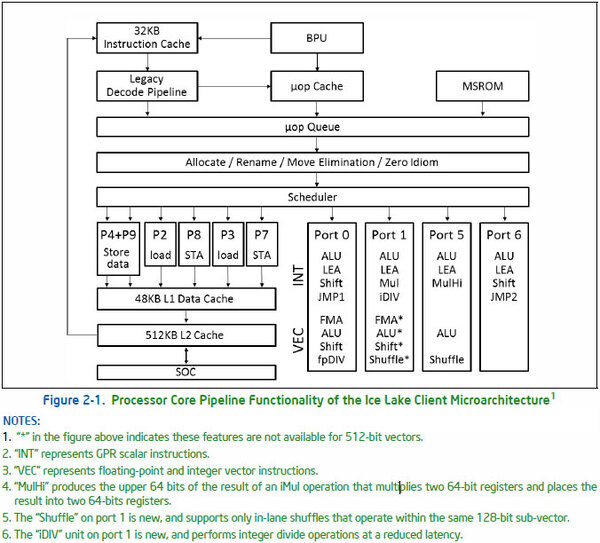

もっとも若干の変更箇所がある。下の画像はクライアント向けIce Lakeの構造であるが、変更点として2つが挙げられる。

なぜか上の画像と左右が逆になっている。ちなみにこれは最新版の一つ前(042b)でのものだが、最新版(043)でも同じ

画像の出典は“Intel 64 and IA-32 Architectures Optimization Reference Manual”のFigure 2-1

- Ice Lake-SPではPort 5に2つ目のAVX512 FMA Unitが追加された

- L2 Cacheが512KB→1.25MBに増量された

Out-of-orderのWindow SizeやScheduler Entries、In-fligh Loads/Storesの数などはクライアントと変わらないが、これはこのあたりに手を入れるとバランスの調整が大変になるためと思われる。TLB(Translation Lookaside Buffer)のサイズなども一緒である。

Sky Lake-SPから比べるとL1 Data Cacheのサイズも増えるなど、全般的にバッファを大きめにしている感じが強いが、これはプロセス微細化で利用できるトランジスタ数が増えたことも大きな要因だろう。

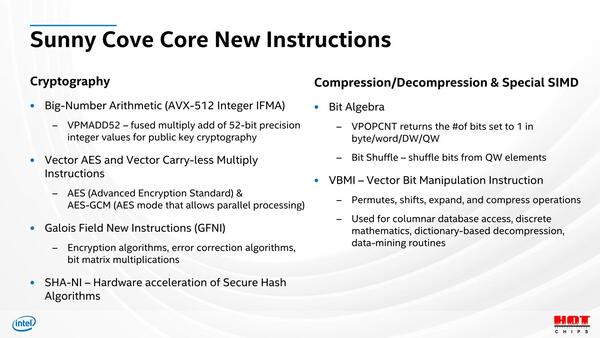

新たに追加された命令に関しては、これはクライアント向けのIce Lakeと違いがない。

新たに追加された命令はIce Lakeと同じ。GFNIは連載538回のTremontの説明の際に触れた

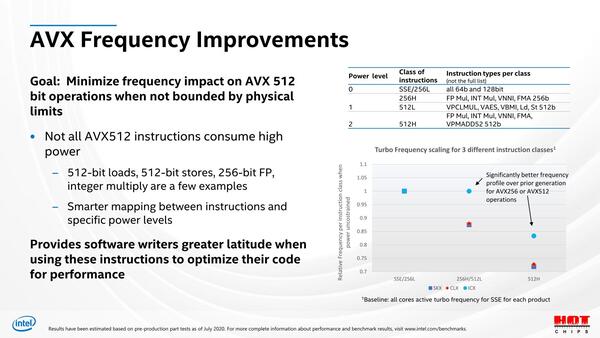

なお、コア周りで言えば省電力関連でいくつか変更や新機能がある。まずAVX Frequency Improvement。

もともとSkylake-SPの時代から、AVX256/AVX512をフルに使おうとする場合、動作周波数を若干引き下げる必要があった。これがIce Lake-SPでは、完全ではない(512Hでは多少下がる)ものの、256H/512L系の命令では動作周波数を下げずに実行可能になった。

SSE/256L、256H/512L、512Hという3つのパワーレベルに応じて動作周波数が変わるAVX Frequency Improvement。ちなみにコンシューマー向けではAVX Offsetといった名前でBIOS Setupに項目が用意されていた

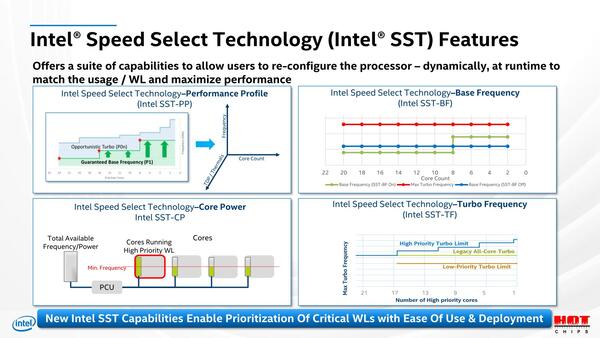

またSpeed Select Technologyが4種類の手法を選べるようになったのも新機能の1つである。

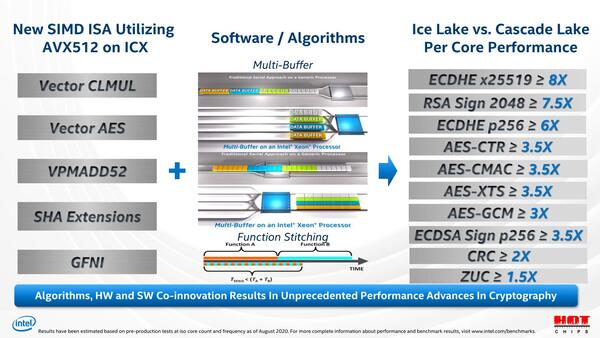

ちなみに詳細な説明がなかったので今ひとつインプリメントが筆者も理解できていないのだが、新たにMulti-Bufferなる手法を利用可能になった「らしい」。

要するに複数のデータストリームを並行してFetchできるようになったため、AVXやSHA/GFNIといった処理においては大幅に性能が改善されるらしいのだが、このBufferというのが物理的にどこの話で、どういう命令を使うとこのMulti-Bufferが実現できるのか、は今のところ定かではない。

このあたりはSoftware Optimization ManualがIce Lake-SPに対応して、もう少し具体的な説明が出てくるのを待つしかなさそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ