3週連続で恐縮だが、やっとAMDがRenoirことRyzen 4000 Mobileの詳細を明らかにするとともに、「AMD、ゲーミングノートパソコン用プロセッサー『AMD Ryzen 9 4900H』発表」のとおり新製品の発表も行なった。このあたりを整理して解説したい。

連載548回で予想した

ダイサイズの答え合わせ

Renoirについては連載548回で、CESにおける発表を解説したが、4ページ目と5ページ目で、ダイサイズおよび内部ブロックの推定を試みた。

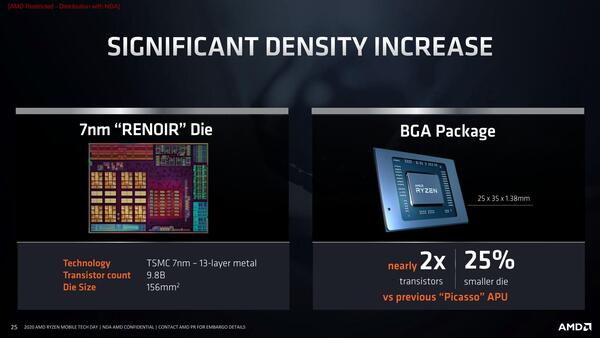

さて、今回こちらの正解が発表された。ダイサイズは156mm2で、140mm2前後という筆者の推定が激しく(1割ほど)ずれていた計算になる。

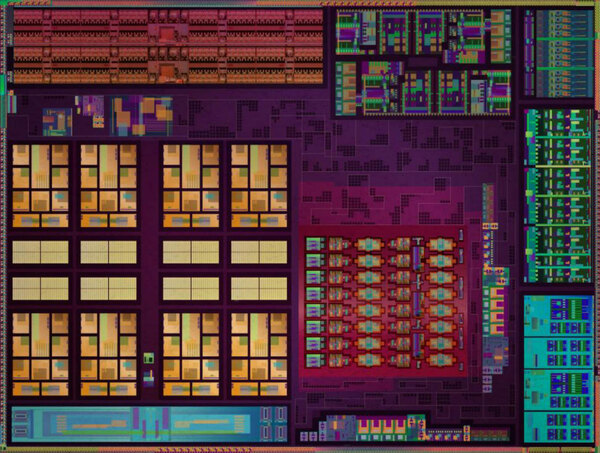

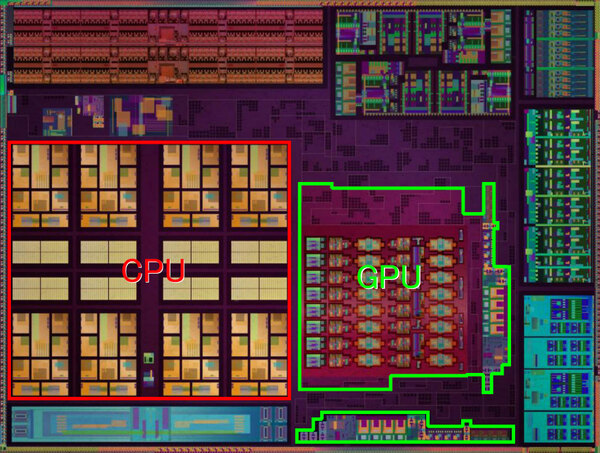

ちなみにこのダイ写真を別のスライドから取ったのがこちら。

ここからCPUとGPUの面積を推測したところ、下表のとおりとなった。

| CPUとGPUの面積 | ||||||

|---|---|---|---|---|---|---|

| CPU | 42.3mm2 | |||||

| GPU | 26.4mm2 | |||||

CPUに関してはMatisseのダイの3次キャッシュを縮めてそのまま収めた感じだが、GPUに関してはフロント(Shader Engine+L2)は一塊にし、バックエンドを2つに分けて実装しているように見える

CPUについては連載548回でほぼ42mm2と推定しており、これが一致した格好だ。

ただGPUは連載548回で40mm2ほどと想定していたのだが、実際にはこれをはるかに下回る26.4mm2ほどになった。実際連載548回で紹介した7nm VEGAの写真と比較すると、整然さに欠けるというか、より面積の最適化を図ったようだ。ただ逆に言えば、その他の機能の実装が予想以上にエリアサイズを食っていたということになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ