動作周波数を上げずに性能向上を目指した

POWER7

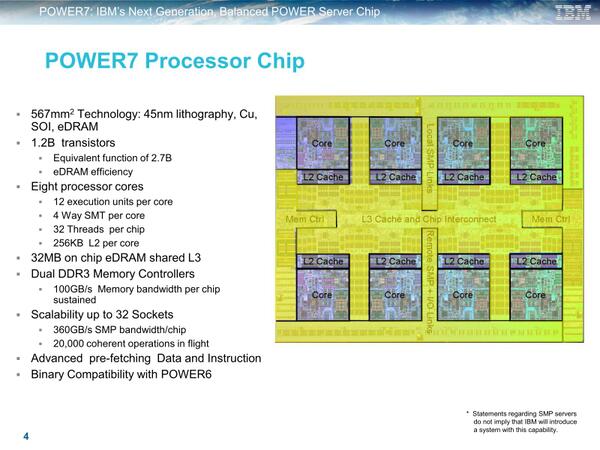

POWER7では1つのダイに8コアと、さらにeDRAMの形で32MBの3次キャッシュを搭載することで、POWER6の1ノード分を1個のダイに収めることに成功する。またSMTもPOWER6までの2wayからPOWER7では4wayに強化されることになった。

画像の出典は、HotChips 21におけるRonald Kalla氏(POWER7 Chief Engineer)とBalaram Sinharoy氏(Chief Core Architect)の“POWER7: IBM's Next Generation Server Processor”

eDRAMが大きなトピックになっているのは、eDRAMの場合1bitのセルが原理的にトランジスタ1個で済むこと(SRAMでは通常6つ必要)で、仮に3次キャッシュを全部SRAMで構成したら、総トランジスタ数が27億個となり、おそらくダイサイズも800mm2を超えると思われるところが、eDRAMにしたことで12億トランジスタ、567mm2で済んだからである。

その分動作周波数はやや低めで、一番周波数の高いPOWER 795に搭載されたモデルでも定格3.75~4GHz、コア数を半分に減らしたTurboCore Modeでも4.25GHzどまりとなっている。

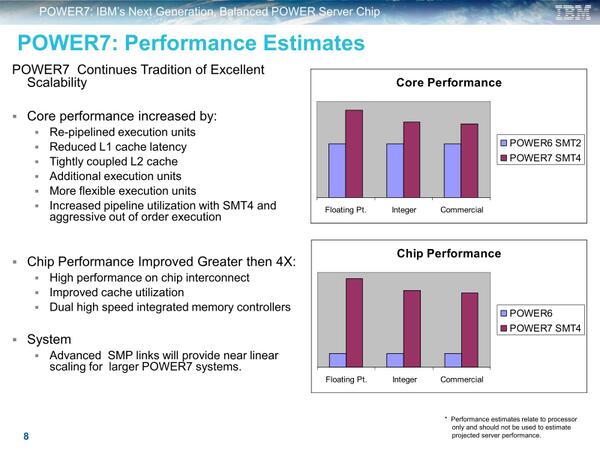

3次キャッシュを統合したのはもう1つメリットがあり、これによって3次キャッシュアクセスのレイテンシーが大幅に抑えられることになった。

POWER6では、2次キャッシュまでは高速にアクセス可能であるが、3次キャッシュになるとオフチップになってしまい、ここでいきなりレイテンシーが急増、結果として演算性能の足を引っ張ることになっていた。この足かせがPOWER7では大幅に緩和されることになり、結果としてスレッドあたりの性能も向上している。

画像の出典は、HotChips 21におけるRonald Kalla氏(POWER7 Chief Engineer)とBalaram Sinharoy氏(Chief Core Architect)の“POWER7: IBM's Next Generation Server Processor”

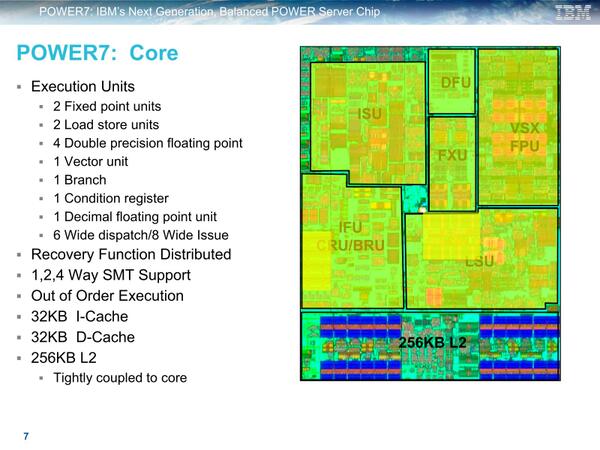

パイプライン自体にも手が入っており、最大で6命令同時解釈/8命令同時発行、実行ユニット自体は12という、かなり重厚な構成になった。この結果であるが、コアあたりの性能はおおむね20%程度、チップあたりの性能は4倍近くに向上した、というのがIBMによる報告となっている。

画像の出典は、HotChips 21におけるRonald Kalla氏(POWER7 Chief Engineer)とBalaram Sinharoy氏(Chief Core Architect)の“POWER7: IBM's Next Generation Server Processor”

1スレッドあたりの性能比較はないが、そもそも実行ユニットがだいぶ増やされていることもあり、同一動作周波数であれば若干の性能改善が見られていると思われる。

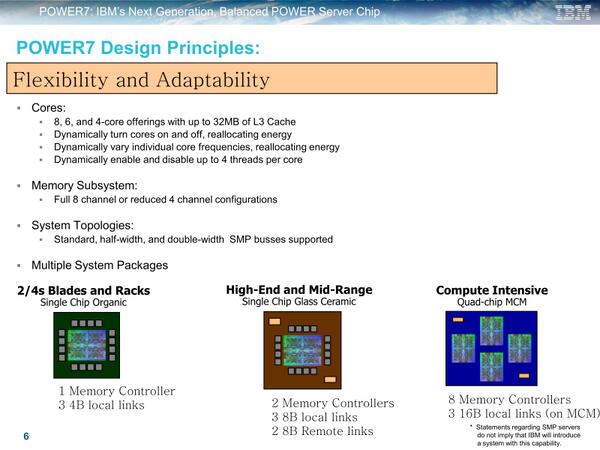

POWER7ではパッケージが3種類用意された。ハイエンド向けには再びMCMが復活しているが、これまでと異なりオフチップのキャッシュ(この場合で言えば4次キャッシュ相当)は搭載されない。

画像の出典は、HotChips 21におけるRonald Kalla氏(POWER7 Chief Engineer)とBalaram Sinharoy氏(Chief Core Architect)の“POWER7: IBM's Next Generation Server Processor”

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ