32nm SOIに微細化したPOWER 7+は

3次キャッシュをさらに増強

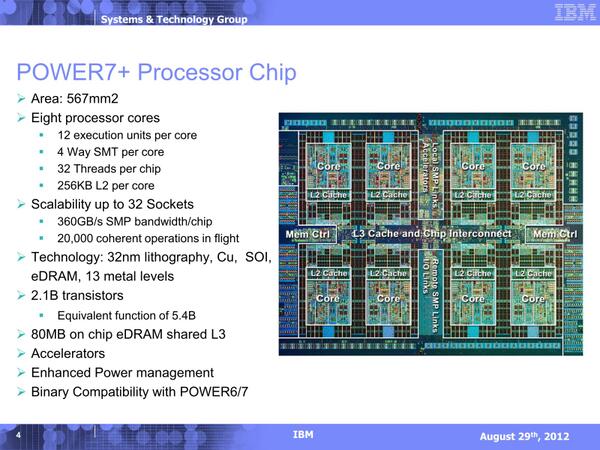

2012年には、POWER 7を32nm SOIに移行させたPOWER 7+も発表されている。コアの数こそ8つのままだが、eDRAMを利用した3次キャッシュは80MBに増強された。

画像の出典は、HotChips 24におけるScott Taylor氏の“POWER7+”

また最大32ソケットまでのSMP構成に対応しており、最大構成では256コア/1024スレッド動作となる。もっとも動作周波数の方は定格で最大3.86GHz、TurboCoreモードで4.14GHzとやや控えめになっている。

このPOWER7を搭載したモデルは2010年2月にエンタープライズ向けのPower 750 Express~Power 780がまず登場、同年4月にブレードサーバー向けのBladeCenter PS700~PS702が、8月にエントリ向けのPower 710 Express~740 Expressがそれぞれ追加される。エンタープライズ向けハイエンドのPower 795もやはり8月に発表された。

そして2012年10月にはPOWER7+を搭載したPower 770/780が発表された。

POWER 8ではパイプラインをワイド化し

1スレッドあたり性能が1.6倍アップ

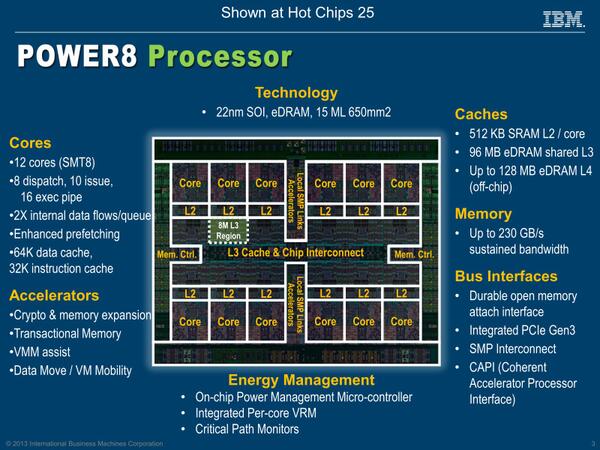

さて、これに続くのが2014年に発表されたPOWER8である。POWER8の部分的な説明は2013年のHotChips 25で行なわれたが、全貌は2014年のHotChips 26で明らかにされた。

まず2013年に明らかにされたPOWER8の構成は以下のようになっている。1ダイあたり12コアで、各コアが8way SMTなので、つまりダイ1個あたり96個のスレッドが動作するお化けと化している。

画像の出典は、HotChips 26におけるAlex Mericas氏(Systems Performance, IBM Systems & Technology Group Development)の“Performance Characteristics of the POWER8 Processor”

製造は22nm SOIであるが、ついにeDRAMは96MBになった。ただPOWER7が10コア/80MBなので、コアあたり10MBの3次キャッシュだったのが、POWER8では12コア/96MBでコアあたり8MBとやや減少している。加えて同時稼働スレッドの数が倍だから、どう考えても3次キャッシュ不足である。

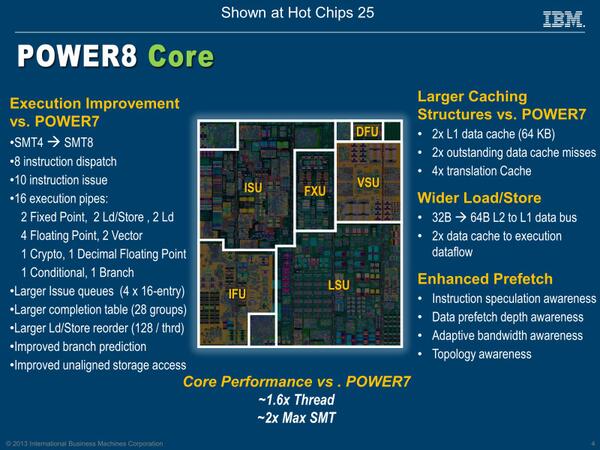

このため、外部に128MBのeDRAMを4次キャッシュとして接続できる仕組みとなった。コアそのものも、8way SMTということもあってさらに幅広なパイプライン構造になった。

画像の出典は、HotChips 26におけるAlex Mericas氏(Systems Performance, IBM Systems & Technology Group Development)の“Performance Characteristics of the POWER8 Processor”

1次キャッシュの大容量化や1次/2次キャッシュのバスの広帯域化などはほぼセオリー通りというところ。こうしたパイプラインのワイド化は当然1スレッド性能の向上にもつながるわけで、最大1.6倍とされる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ