前回のロードマップアップデートは昨年6月だったので、実に14ヵ月ぶり(回数で言えば60回ぶり)にNVIDIAのロードマップである。

Turing世代のGPUが発表

レイトレーシングの処理をハードウェアで実装

既報の通り、NVIDIAは8月20日にTuringアーキテクチャーを搭載したGeForce RTX 2080Ti/2080/2070の各製品を発表した。

おそらくKTUこと加藤勝明氏がGeForce RTX 2080Tiを、ジサトライッペイ氏がGeForce RTX 2080を2枚購入するのだろうとは思うが、それはさておき、長らく動きがなかったNVIDIAのコンシューマー向け製品がやっと刷新されることになったのは素直に喜ばしい。Titan XpやGeForce GTX 1080Tiから1年弱、GeForce GTX 1080は2016年5月の発表なので実に2年以上の沈黙を破ったことになる。

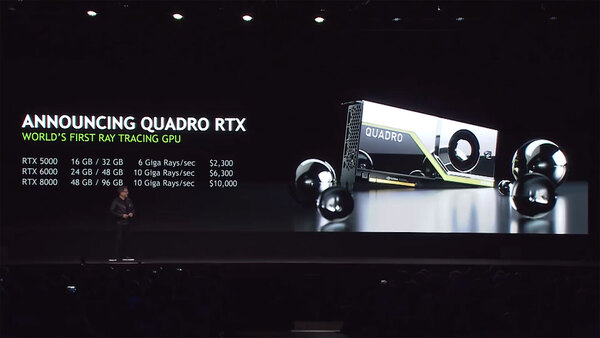

さてそのTuring世代だが、最初にアナウンスされたのはGamesconの前週にカナダで行われたSIGGRAPH 2018で発表されたQuadro RTXである。発表会の中継はYoutubeに上がっているので、ここからいくつかの情報をピックアップしてまずは特徴を解説したい。

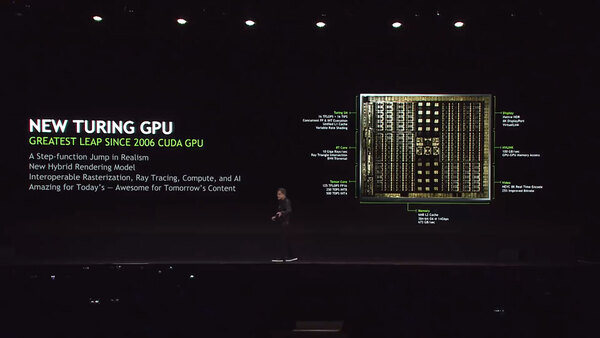

Quadro RTXはTuringベースのハイエンドコアを実装した製品で、この数字はいずれもQuadro RTX 8000の数字をベースにしたものと思われる。

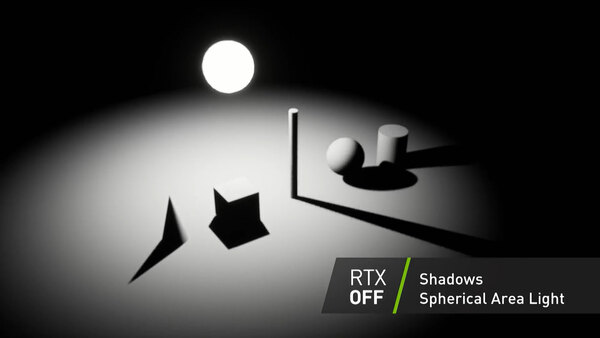

特徴なのはレイトレーシングの処理をハードウェアで実装しており、これが最大10G Rays/秒とされる。レイトレーシングは、光源から出る光がどこにどう反射して最終的に目に入るかを追跡していくという方法で、特に金属表面の映り込みなどでその効果はてきめんである。

わかりやすいのは下の動画の31秒あたりから。ポルシェの表面に、流れる光が反映して映り込む様子がわかるかと思う。このあたりの細かい話はKTU氏の記事が詳しいので一読をお勧めする。

もっとも光源から追っかけていくと計算量が膨大になりすぎるので、通常は視点から逆に光源までを追っかける形になるが、それでも計算は膨大になる。

CPUでこれを実装した例がPOV-Rayで、たとえば先日Ryzen Threadripper 2990WXを利用した場合には最大で10000pps(毎秒10KPixel)の描画が可能、という結果が出ていたが、10KPixelということはVGA(640×480ピクセル)の一画面をレンダリングするのに30.72秒ほどかかる計算になる。これは到底ゲーミングなどには使えない。

ところがTuringではこれをハードウェアで行なう(この際の光源からの経路を毎秒100億回、計算ができる)という話になっている。

このレイトレーシングの計算を行なうのは独自のRT Coreと呼ばれるもので、従来のCUDAの演算ユニットそのものとは別に実装される形になる。

それとは別に従来の整数/浮動小数点演算ユニットが用意されているが、最初の画像でも16TFlops+16TIPSとあるように、整数演算と浮動小数点演算を同時にできるようになっている。

またAI関連ではTensor Unitが用意されており、最大で500T Tensor Opsとなっているわけだが、これはトリックがあり、Photo08の左下にあるように500T Ops/秒はInt 4(4bit整数)の場合のみ。Int 8(8bit整数)では250T Ops/秒、FP16では125T Ops/秒となっている。

これに関しては、VoltaのTensor CoreはFP16で120T OPS/秒とされているから、実はAIに関しては(精度が同じなら)あまり性能は上がっていないことになる。

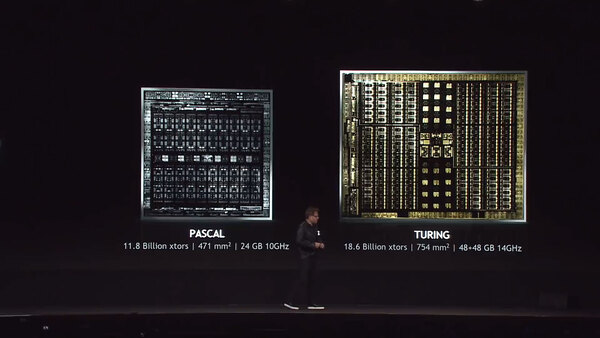

発表では上の画像のようにPascalとのダイの比較もあったが、ラフにトランジスタ密度を比較してみると以下のようになる。

Pascal:118億トランジスタ/471mm2=250.5万トランジスタ/mm2

Turing:186億トランジスタ/754mm2=246.7万トランジスタ/mm2

ほとんど変わらないことを考えると、製造プロセスそのものは引き続きTSMCの12FFNが利用されているものと思われる。いくらなんでも、今のTSMCが7nmで700mm2を超えるダイを量産できるキャパシティーがあるとは思えないから、この推定は妥当だろう。

ちなみにラインナップとしてはQuadro RTX 8000に加えて5000/6000も用意される。ただこれがまた恐ろしいのは最大48GBのラインナップが用意されることだ。

プレスリリースにもあるように、Quadro RTX 8000はSamsungの16Gbit GDDR6メモリーを搭載している。つまりチップあたり2GBだから、48GBにするためにはGDDR6チップを24個搭載する形になる。

おそらく基板の表裏にそれぞれGPUを囲むように12個づつ配しているものと思われる(それぞれが16bit接続で、バス幅は384bitと推定される)が、なかなか凶暴な配置ではある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ