Sandy Bridge以降のCore iシリーズは

すべてRing Busを採用

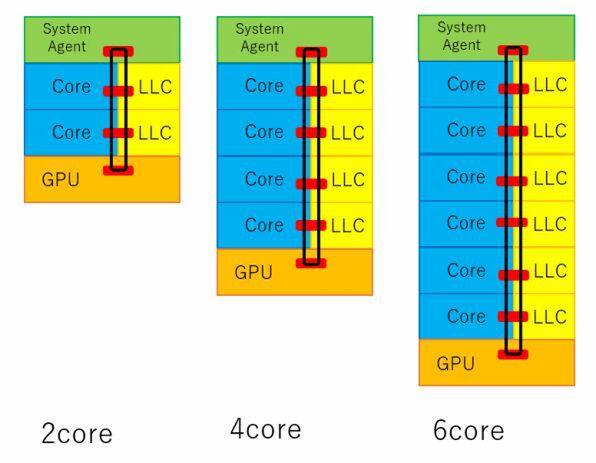

XeonではRing Busを廃した一方で、コンシューマー向けのCore iシリーズ(除くCore-X)については、Sandy Bridge以降Ivy Bridge、Haswell、Broadwell、SkyLake、KabyLake、CoffeeLakeではすべて、Ring Busを利用している。下図がその内部構造で、System AgentとGPUの間にCPU CoreとLLCを挟み込む形でどんどん数を増やしているのがわかる。

単純にコアを増減させるだけなら、Ring Busは共有バスと同じ程度に簡単に変更できるのが大きなメリットというわけだ。 ちなみにインテルのSkylake-SPやCore iシリーズで採用されているのは、いわば「擬似二重Ring」構成である。

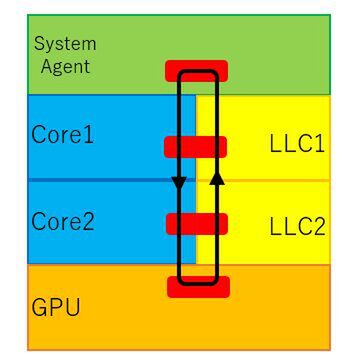

下図は2コア製品の拡大図である。中央の黒い輪がRing Busで、これは一方向にしかデータが流れない。ただし、Ring Stop(赤い部分)に関しては、2つのコアは上りと下りの2方向につながっている。

Core iシリーズ2コア製品の拡大図

たとえばCore 1からみると、Core 2あるいはGPUに通信したい場合は下り方向に、System Agentに通信したい場合は上り方向にデータを流せば、最小のレイテンシーでデータが送られるというわけだ。

一見良さそうに見えるが、この方式では両端にあるGPUとSystem Agentは事実上Ring Stopが1つしかないわけで、たとえばCore 1とGPU、あるいはCore 2とSystem Agentの通信は短縮できない。もっと問題なのはGPUとSystem Agentの通信で、これはCPUコアの数だけレイテンシーが増えることになる。

この擬似二重Ring方式は、CPUの数が6個くらいが現実問題としては限界に近い(8個も実現できるとは思うが、やや性能へのインパクトがありそうだ)。したがって今後メインストリーム向けに8コアが普通に登場するようになると、多少構成が変わるかもしれない。

ただ4コア以下に関してはきわめて合理的な方法であって、拡張性をある程度無視できるなら最適な方法である。インテルがRing Busを使い続けるのはこのあたりが理由であろうし、逆にAMDはZenで当初から8コアを想定していたので、Ring Busは最初から考慮に入ってなかった、というあたりではないかと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ