Ryzen 7のダイを4つ搭載したMCMが

Naplesか?

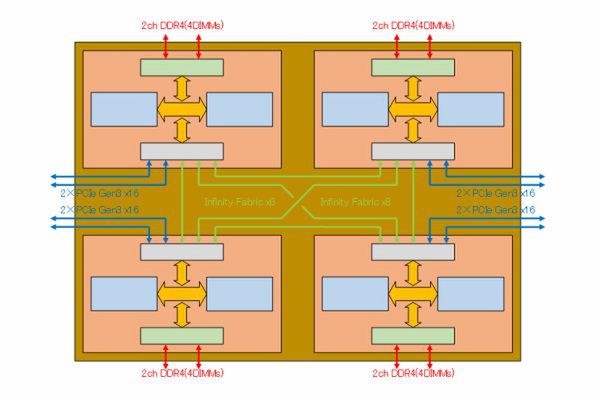

ではNaplesは? というと、ずばりこのRyzen 7のダイを4つ搭載したMCM(Multi-Chip Module)になるだろうと筆者は考えている。

このケースでは、各々のダイからメモリーチャンネルが2本づつ、PCI Express Gen3が32レーンづつ出る形になる。それとは別に、各コア間の接続にSerDesをx8レーンを利用しての接続が行なわれていると思われる。

このあたりはOpteronの4ソケット構成に近いのだが、Opteronの場合はプロセッサーあたり3本のHyperTransport Linkが出つつも、うち1本はチップセットの接続に必要で、完全対称型にはできなかったのだが、Naplesの場合はそれぞれのRyzenのダイから外向けのPCI Expressとは別に32レーン分のI/Fがあり、このうちの3本を相互接続に使うことで完全対称型の接続が可能になっていると思われる。

これでは、まだSerDesが8レーン残ってることになるが、AMDによるNaplesのプレビュービデオの1分40秒手前あたりで、「チップセットが要らなくなった」としている。

上の予想図には示していないが、おそらくNaplesは4つのRyzenのダイ以外にサウスブリッジにあたるI/Oハブも搭載されており、これとダイの間をあまったx8レーンでつなぐのではないかと筆者は考えている。

この方式のメリットは2つある。まず1つ目は将来ラインナップを作りやすいこと。今回はハイエンドの4ダイだが、1/2/3ダイでも同様の構成が可能である。1/2/3ダイの場合、利用できるメモリーチャンネルやPCI Expressレーンに制限が出てくるという問題はあるが、動かないわけではないからだ。

もう1つのメリットは、コスト面に関する話だ。たとえばNaplesを物理的に1ダイで作ろうとすると、さすがにRyzenのダイのそのまま4倍にはならないにしても、3倍ではきついだろう。現実問題として700mm2を超える巨大なダイになるのは間違いない。当然歩留まりは悪いだろう。

MCMで4ダイ構成にすれば、こうした生産面での懸念はかなり減る。あらかじめスクリーニングしてちゃんと動くダイ4つを後工程でMCM化すればいいからで、MCMを利用することに起因するコスト増を勘案しても十分利益が出ると思われる。

ところで、SerDesとPCI Expressが入り混じっているのは意図的である。SerDesそのものは汎用のもので、最近では1レーンあたり56Gbpsもの転送速度を出すものが普通に存在する。これは特にネットワークの分野で、40/50/100/200/400Gbpsのイーサネットの普及が始まりつつあり、さまざまなメーカーが高速なSerDesを用意しようとしていることに対応するためだ。

たとえばCredo Semiconductorは昨年9月、TSMCの28nm/16FF+/16FFCに対応した56/112GbpsのPAM4対応SerDesを発表している。PAM4というのは信号を4値にすることで、1回の転送で2bitを転送できるようにしたものなので、実質的な信号速度は28/56GT/秒になるが、それでも相当早い。

GlobalFoundriesも同様に、56GbpsのPAM4対応SerDesを14LPPの上で提供することを昨年12月に発表しており、こちらも信号速度は28GT/秒になる。この56Gbps対応SerDesをGlobalFoundriesはHSS(High-Speed SerDes)と称しているが、HSSを利用してたとえばPCI Express Gen4やHBMのI/Fなどを作ることも可能としている。

つまり信号速度は最大28GT/秒(カタログによれば30GT/秒あたりまで行けるらしい)というだけで自在に制御でき、またSerDesの手前にプロトコルや変調を入れることで、さまざまな特定プロトコルに対応できるわけだ。

こうした高速なSerDesを複数搭載しておけば、8GT/秒まで速度を落とし64b/66bの変調を入れればPCI Express Gen3として使えるし、Infinity Fabricとして使うときはもっと速度を上げれば、性能を落とさずに接続できることになる。

先の予想図で4つのダイの間を相互接続するInfinity Fabricの速度がどの程度かはわからないが、あくまでシリコンインターポーザーの上で、しかも距離が短いので信号の振幅はかなり小さくても問題ないはずで、30GT/秒程度の信号転送速度は十分確保できるだろう。

8bit幅なら30GB/秒という計算で、もしなんならPAM4変調も入れれば60GB/秒もの帯域が利用できることになる。内部接続としてこれは十分な速度であろう。

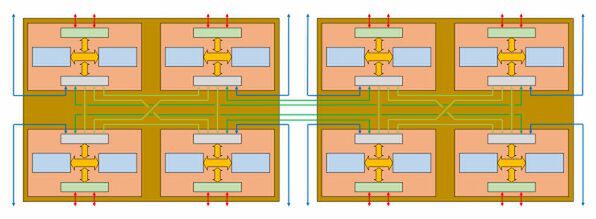

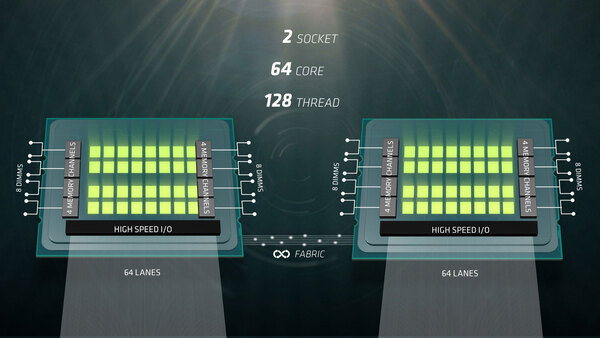

2ソケット構成での予想

さて、次は2ソケット構成である。2ソケット構成の場合、PCI Expressレーンを半減させ、あまった分をInfinityFabricとしてソケット間接続に使う形になっている。その場合の接続はどのようになるのかという、これまた筆者の想定図が下の画像となる。

今度はMCM内部ではなくソケット間、つまり一旦ソケットを経由して基板を通り、再びソケット経由でつなぐ構成になる。こうなるとSerDesそのものは56Gbpsと言っていても、信号経路に反射や減衰の影響になりそうなものが多く介在することになるため、どうしても信号速度は落とさざるを得ない。

個人的には、x16レーンをそのまま使い、速度はMCMの場合の半分(たとえばMCM内部が30Gbpsでつながっているとしたら、ソケット間は15Gbps)に落とすのではないかと思う。ただレーン数はx16で内部接続の倍なので、帯域そのものに違いはない。

この場合、それぞれのRyzenのダイはHyperCubeに近い構造でつながることになる。これはマルチプロセッサーを構成する場合に非常に都合が良いというのはかつてスーパーコンピューターの系譜の連載の中でいくつか事例を示して紹介した通りだ。

強いて言うなら、1ソケット内のインターコネクトに比べると、ソケット間のインターコネクトがやや見劣りするが、これはむしろソケット内のインターコネクトが異様にリッチすぎると考えたほうが妥当な気がする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ