ワンチップに複数コアを組み込む作戦で

Larrabeeを活用

結局インテルはGPUの代替としてLarrabeeを利用することを放棄、既存のIntel GMAアーキテクチャーを引き続き改良し続けることにした。これは妥当というか、適切な戦略であったと思う。ただそれはそれとして、Larrabeeのアーキテクチャーそのものはまだ利用できる、とインテル自身は考えていた。それはまさしくHPC向けの用途である。

もともとインテルはMPP(Massive Parallel Processing:超並列)に広く精通していた。その最初のものはiPSCで、これにParagonが続き、ASCI Redにつながることになる。

これらのシステムは、いずれも汎用のx86プロセッサーを密結合する形でシステムを構築しており、当然その分システムのサイズや消費電力は大きくなっている。ところが、Larrabeeのようにワンチップの中に複数のx86コアが統合される構成なら、1個1個の性能は多少低くても、トータルとしての性能/消費電力比を高めることで、結果的に高性能なシステムを構築可能になる。

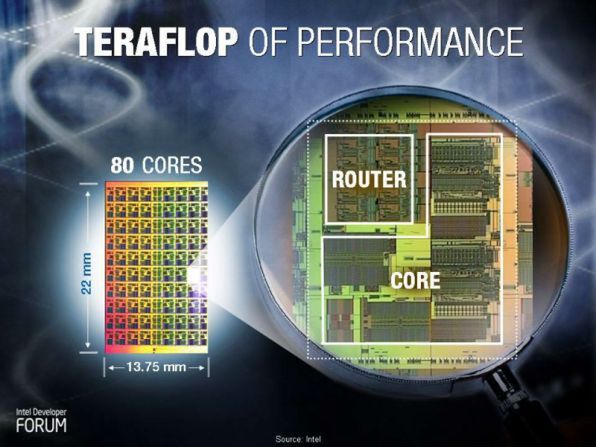

ASCI Redを最後に、大規模なHPC向けシステムをインテルは開発・納入していないが、研究開発チームは継続してこうした研究を続けてきた。その一例が2006年のIDFで発表された80コアのチップである。このコアはx86とは互換性のない独自のものだが、TFLOPSクラスの性能と、3.1GHz動作の場合で10GFLOPS/Wの性能を実現できることを発表している。

ISSCC 2007ではもうすこし突っ込んだ説明があり、1GHz動作で0.32TFLOPS、3.1GHzで1TFLOPS、ピークは5.67GHz駆動で1.8TFLOPSの性能になることが明らかにされている。これはあくまでも試作であって、同じ仕組みがLarrabeeに適用できるわけではないが、ワンチップに複数コアを組み込むMany Coreの方向性とLarrabeeは相性が良い、と判断したようだ。

この結果インテルはLarrabeeの方向性を大きく変更し、HPCに向けたMany Coreのプラットフォームとして活用することにする。とは言え、この時点では大きく2つの要素が欠けていた。1つは絶対性能で、なにしろ16コアしかないため、いくら16wayのSIMDエンジンでもピーク性能はそう高くないし、実効性能はさらに見劣りする。

もう1つは適切なプログラミング環境である。NVIDIAのCUDA、あるいはAMDのBrook+に相当するものを、この時点でインテルはLarrabee向けに提供できていなかった。そこでここから猛然とインテルは欠けているパーツを埋めるべく奔走し始める。続きは次回説明しよう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ