2015年のハイエンドGPUは20nmプロセス

FinFETを使った製品は2016年に投入

それでは、そのトップエンド製品についてみていこう。下の画像はMark Papermaster氏のプレゼンテーションである。

要旨をまとめると以下のようになる。

このうち(1)は主にドライバー側の問題である。すでにGCN世代ではMantleが普通に使えるようになっており、DirectX 12やVulkan、Metalといった新世代APUと原理的には同一の機構なので、あとはAPIだけそれぞれにあわせれば済むことである。Virtual Realityは、これも同社が提供するLiquidVRというソフトウェアの話である。

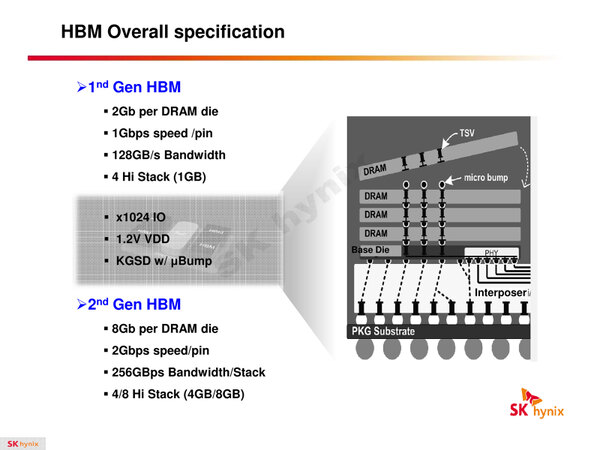

問題は(2)で、これはHBMのことである。HBMの話は散々書いてきたので説明の必要はないと思うが、構成そのものは連載270回で説明したとおりだ。

AMDによればGDDR5と比較して3倍の性能/消費電力比と、50%のパワー削減が可能という。ちなみにそれぞれの数字の根拠がよくわからない。どちらも脚注には“数字はAMD社内の推定値”とあるだけで、なにをどう比較したのかが明らかではないからだ。

おそらく前者はチップ単位の数字で、同じ消費電力ではHBMはGDDR5の3倍の帯域を利用可能というもの。後者は同じメモリ容量の構成にすると、HBMはGDDR5の半分の消費電力で済むというあたりではないかと推測する。

これをどうつなぐかというと、GPUチップと基板の間にSilicon interposer(要するにシリコンベースで製造した緻密な基板)を挟み、このSilicon Interposerで接続する。

この技術はすでにTSMCがCoWoS(Chip-on-Wafer-on-Substrate)という名前で提供を始めており、実際TSMCのCoWoSのプレゼンテーションの中には、GPUとHBMの接続に使う事例まで出てきており、実装そのものは容易だろう。

また連載297回でも説明したとおりHBMの量産そのものはすでにSK Hynixで開始されているため、入手性も問題ない。

つまり、逆説的になるがHBMを採用したことで、2015年のハイエンドGPUは事実上TSMCの20nmプロセスを使うことがほぼ確定したとも言える。16nmでないのは、(3)からも明らかだ。

AMDはFinFETを使った製品を2016年に投入するとしており、逆に言えば2015年中は投入される見込みがないということになる。またAMDは昨年から20nm世代のRadeon製品を投入することを発表しており、28nmの可能性は薄いと思われる。

気になるのは、そこで性能面での改善がどの程度あるかということだが、ここでキーになるのがやはりHBMである。連載269回で説明したとおり、NVIDIAは1一度20nm世代への移行を進めたものの、性能面での優位性がない(むしろ性能が悪化する)ということでこのプランを丸ごとキャンセルして28nmから16nm FinFETという形に製品展開を切り替えた。

実はAMDについても、同じ状況になりえる可能性がある。ただ幸いなのは、NVIDIAは引き続きGDDR5を使うつもりだったためメモリー帯域の改善はあまり期待できず、コアの性能が上がらないと全体的な性能改善にはつながらなかったのだが、AMDの場合はここでHBMを投入するので、メモリー帯域が数倍増えることになる。

極端なことを言えば、GPU側のコアが一切変化なくても、メモリー帯域が2倍になれば性能は倍とは言わないまでも50%くらいの底上げが可能になるわけで、加えて20nmに微細化することで、同じダイサイズならば利用できるトランジスタ数が90%増加するとしている。

実際には配線もあるし、熱密度もあるためここまでトランジスタ数は増えないだろうが、それでもCU数を4~5割増にできる程度には期待できるだろう。

動作周波数はやや落ちるだろうが、その分CU数が増えているからGPUの性能比では2割増程度になり、これとHBMの相乗効果で50~60%のトータル性能改善というのは、そう無茶な推定ではないだろう。

ただし当初はGPU、CoWoS、HBMとすべての部材が28nm世代より高くつくので、どうしても製品価格はそれなりになる。したがって当面はR9 290やR9 290Xの後継製品のみということになるだろう。

このGPU+HBMの構成がメインストリーム向けまで展開するのは2016年からというあたりになると思われる。R9 380以下が全部リナンバリングにならざるを得ないのも仕方ないところかもしれない。

その2016年だが、こちらは16nmのFinFETか、実際には16nm FinFET+に移行し、かつGCN自身にも若干の改修が加えられて、2倍の性能消費電力比(*)を実現するほか、HBM自身も第2世代のものを利用するとしている。

(※)AMDはこの2倍の比較対象を“Previous Generation GCN Architecture”としているが、28nm世代なのか、それとも20nm世代なのかははっきりしない。おそらく28nm世代の現行製品と比較して、ということだろう。

第2世代のHBMはどういうものなのかは、SK Hynix自身がすでに公開しており、DRAMチップ自身の容量が4倍、転送速度そのものが2倍になった製品である。

今のところまだ第2世代HBMはサンプル出荷も開始されていないが、AMD自身もこの16nm世代製品をリリースするまでまだ1年以上あると思われるので、それほど問題はないだろう。

ということで、今回は詳細なロードマップはないが、これについてはCOMPUTEX後あたりのタイミングでまたまとめたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第876回

PC

このままではメモリーが燃える! HBM4/5世代に向けた電力供給の限界と、Samsungが示すパッケージ協調設計の解 -

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 - この連載の一覧へ