前回に引き続き、今回もARMの新64bitコア「Cortex-A57/A53」について解説したい。だが本題に入る前に、少し最新情報を追加しておきたい。

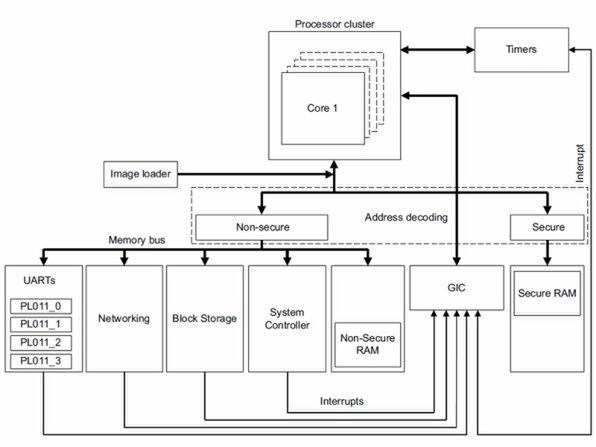

まずARMは11月20日に、「ARMv8 Foundation Model」と、これのマニュアルを公開した。Foundation Modelとは、非常に簡単なARMv8プロセッサーのエミュレーターである。現在のエミュレーターのバージョンはまだv0.8だが、最大4コアのプロセッサーと最大8GBのRAM、UART(シリアル通信ポート)にネットワーク、Secure RAMなどのエミュレーションが可能であり、これで早速ARMv8のプログラム開発が始められるというわけだ。

これにより、システム開発者はこのエミュレーターを使って、ARMv8に対応したアプリケーションの基本部分の開発を始められる。もちろんエミュレーターでしかないから、この上でパフォーマンスチューニングをやるのは論外だし、あくまでも基本的な周辺回路しか搭載されていないから、複雑なデバイスに対応するアプリケーションの作り込みなども無理だ。だが基本的な部分、例えばOSカーネルや基本的なライブラリなどの移植には、とりあえず使えるレベルである。

ARMの場合、SoCがどんな構成になるのかはプロセッサーメーカーごとに異なるから、ARM提供の開発キットが全部を網羅するのは不可能である。また、ARMからCortex-A57/53コアのライセンスを受けたメーカーは、それにどんな周辺回路やバスを組み合わせて自社のSoCを作るかを決める際に、性能評価のためにもっと本格的なシミュレーターを動かす必要がある。完全に構成が決まると、本核的なシミュレーターがそのままソフトウェア開発のプラットフォームとして利用できるので、ARMのエミュレーターはそれまでの間だけ使えればいいわけだ。

公開されたCortex-A57/A53の概要

では本題に入ろう。10月末の開発者向けイベント「ARM TechCon 2012」にて、ARMは正式にCortex-A57/A53という2種類のCPUコアを発表した。この2つのコアの特徴をまとめると以下のようになる。

プロセッサーアーキテクチャー

どちらもARMv8準拠で、ARMv7互換の32bitアドレス命令「AArch32」と新しい64bitアドレス命令「AArch64」に準拠。セキュリティー機能として「TrustZone」、SIMD拡張として「NEON」に対応するほか、「VPFv4」と呼ばれる浮動小数点演算命令と、ハードウェア仮想化機能を搭載する。

これにともない、仮想アドレスは64bitに拡張されたほか、新たに汎用レジスタが31個に増強された(ARM v7までは15個)。当然レジスタサイズも64bit幅に拡張されている。またAArch64ではさらに、以下のような項目が追加されている。

- SIMD演算の倍精度浮動小数点対応

- 相対アドレス指定幅の拡張。「Tagged Pointer」と呼ばれる方式への対応などの、アドレス指定方式の拡張

- 64KBのページサイズに対応

- キャッシュ管理方式の拡張

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第876回

PC

このままではメモリーが燃える! HBM4/5世代に向けた電力供給の限界と、Samsungが示すパッケージ協調設計の解 -

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 - この連載の一覧へ