9月3日のIvyBridge-Eこと「Core i7-4960X」に加え、11日(米国時間)にはXeon向けのIvyBridge-EPが公式に発表になった。そこで今回はIvyBridge-EPについて解説したい。

3種類ものダイが存在する

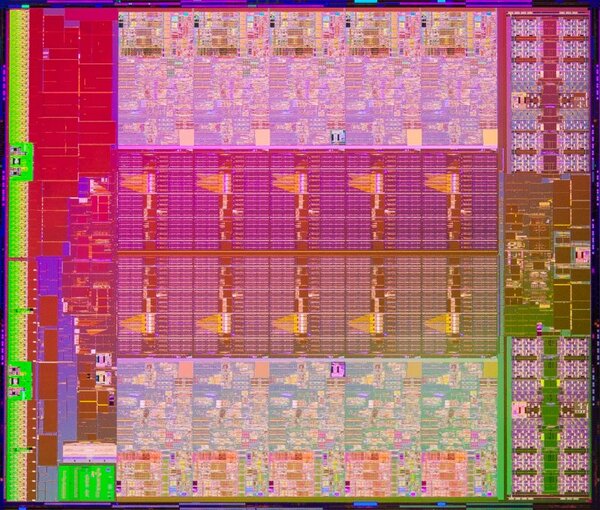

IvyBridge-EP

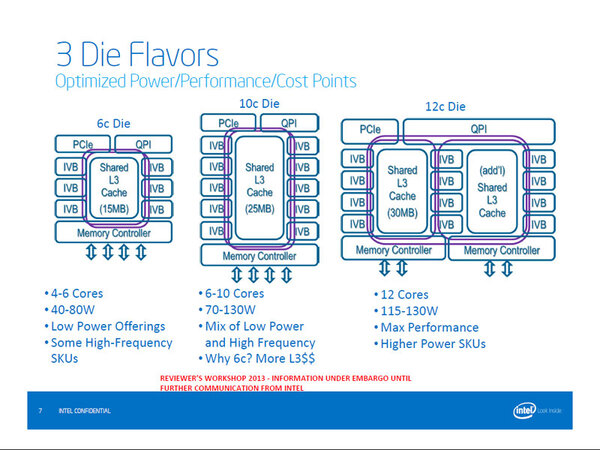

今回発表された製品は4コアから12コアまでラインナップが広く展開されている。ラインナップ詳細はこちらを見ていただくのが早いが、さすがにこれだけあると、ダイの種類もSandyBridge-Eのように1種類だけだとやや効率が悪い。そこでIvyBridge-EPではコアの種類を3つ用意した。

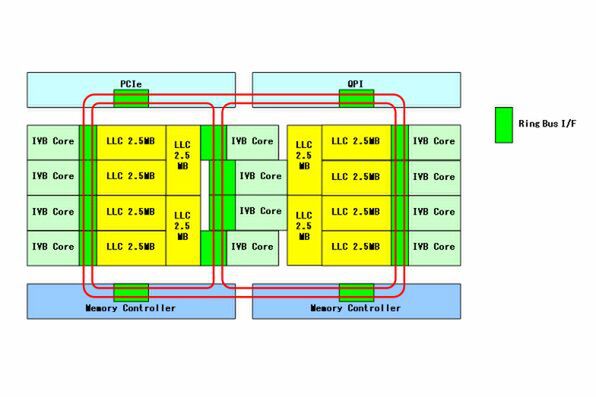

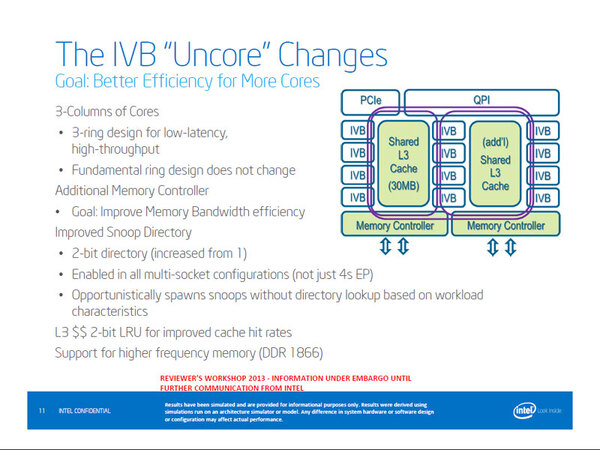

やはり12コアともなると、6コア/12コアと同じリングバス構成ではややレイテンシーが長くなると判断されたのだろう。ここでわかりにくいのが12コアにおけるLLC(3次キャッシュ)の構成であるが、下図のようになっているそうだ。

中央の4つのコアは、それぞれ左右に振り分ける形でLLCを搭載している。「Core i7-4960X」を初めとするIvyBridge-Eコア製品は、この6コアのものをそのまま流用する。

SandyBridge-EPとの違いは

DDR3-1866対応かどうか

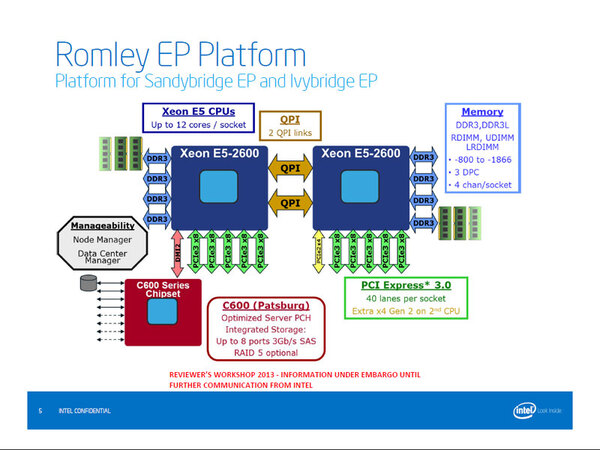

プラットフォームそのものは、既存のLGA 2011がそのまま利用される。基本的にはマザーボードのBIOSアップデートだけを行なえばそのまま利用できることになっており、実際IvyBridge-Eベースの「Core i7-4960X」では、既存のX79マザーボードのBIOS アップデートだけでOKとなっている。

もともとSandyBridge→IvyBridgeそのものがインフラをそのまま使えており、これがSandyBridge-EP→IvyBridge-EPでも継承されたということだ。

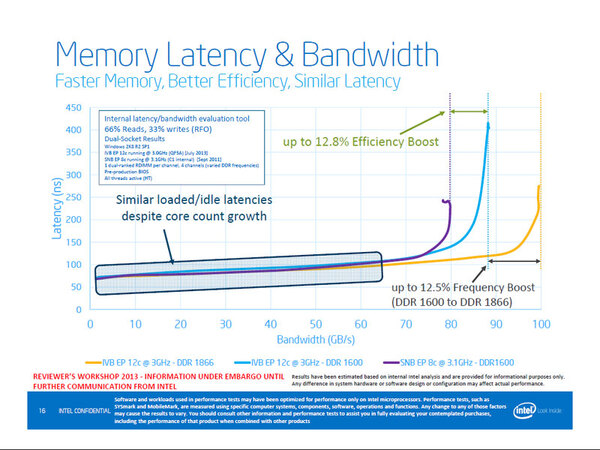

唯一の違いは、従来のSandyBridge-EPでは公式にはDDR3-1600までの対応だったのが、IvyBridge-EPではDDR3-1866に対応したことだろう。メモリーチャネルあたり3DIMMまでというのは最大値であり、DDR3-1866では1枚か2枚に制限されることになるだろう。

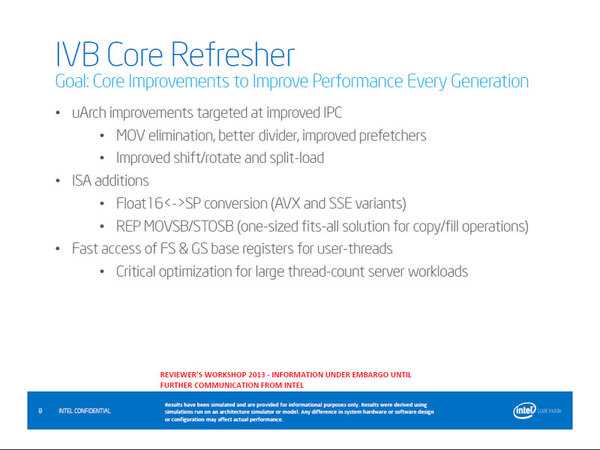

CPUコアそのものはデスクトップ向けのIvyBridgeとまったく同じであり、いくつかの命令拡張などはあるものの、基本的には従来のSandyBridge-Eと変わらない。したがって相違点としては、22nmプロセスによる省電力化と、これによる動作周波数の向上、あとはUncore部分の変更ということになる。

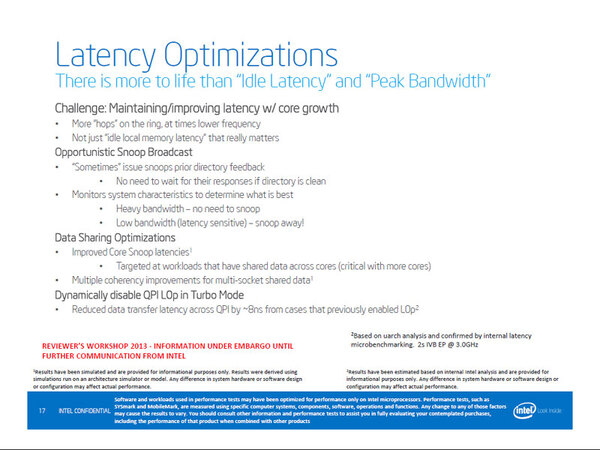

まずそのUncore部の1つ目が下の画像だ。12コア製品で3列構成となったほか、DDR3-1866のサポート、それにキャッシュのスヌーピング(キャッシュ間の一貫性を保つ仕組み)の改善が挙げられる。

このキャッシュのスヌーピング、従来1bitは「変更された/されない」のみで管理していたのを、2bitに拡張してより柔軟な管理ができるようにした。

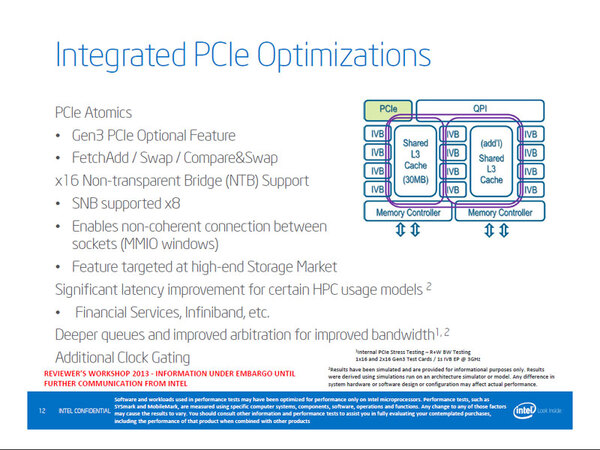

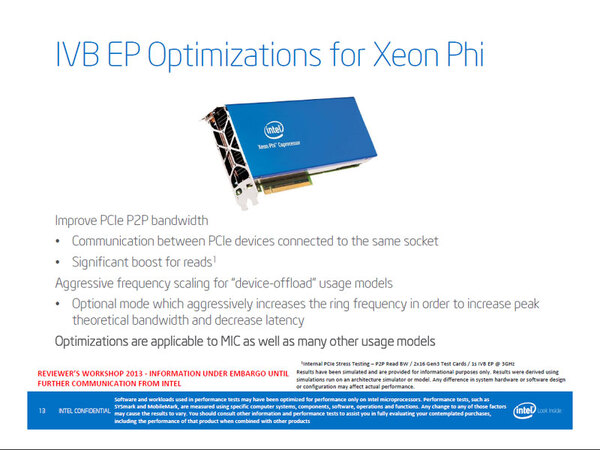

またPCI Expressに関しても、PCI Express経由での接続帯域を増やしたり、Xeon Phiを接続する際に帯域拡張/レイテンシー削減を実現した。

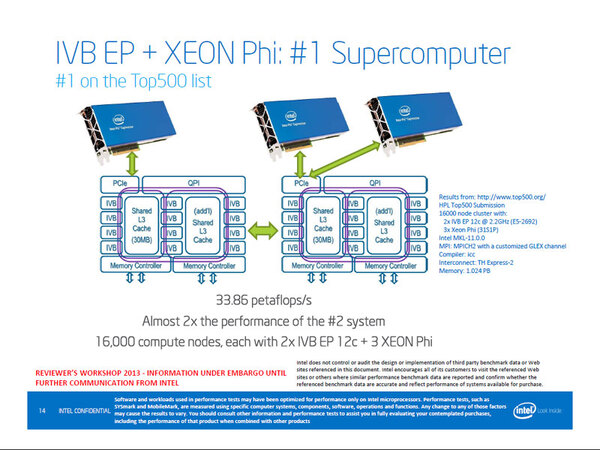

この帯域拡張/レイテンシ削減はどうやって実現したかというと、動作速度の向上である。PCI Express Gen3の場合、信号速度は8GT/秒となっているが、IvyBridge-EPにXeon Phiを接続する構成に限って、信号速度をこれより高める(どのくらい高めるのかは説明がなかった)ことで性能を改善するというものだ。インテルによれば、これによって今年6月のTOP500で1位の成績を実現できた(関連記事)としている。

メモリーコントローラー周りでは、DDR3-1866のサポートによって性能と、レイテンシーの両面で改善があったとするほか、レイテンシーに関してはいくつかの改善策が取られていることも示された。

この連載の記事

-

第781回

PC

Lunar LakeのGPU動作周波数はおよそ1.65GHz インテル CPUロードマップ -

第780回

PC

Lunar Lakeに搭載される正体不明のメモリーサイドキャッシュ インテル CPUロードマップ -

第779回

PC

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ -

第778回

PC

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ -

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 - この連載の一覧へ