クロックゲーティングの導入で

消費電力の削減に成功したBanias

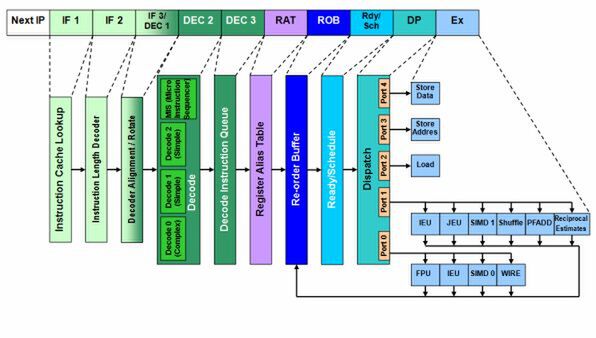

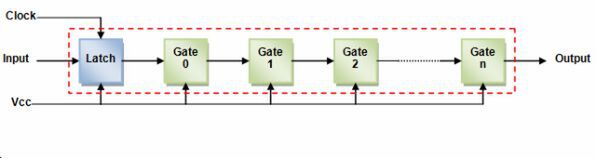

2つ目の改良点が、「クロックゲーティング」である。図3は、基本的なロジック回路を簡略化した図である。まず大前提として、最近のロジック回路は「同期回路」で構成されている。「同期」というのは、「外部から入力されるクロック信号に合わせて、データの送受信を行なう」という意味である。図1のIF1からEXまで10段の各ステージは、すべて1サイクルで処理を終わることを前提としている。その各ステージが、図3の赤枠内に相当する。パイプラインの各ステージは、実際は複数のゲート回路(論理回路)で構成されているが、ステージ全体がひとつと見なした図である。

同期回路では外部からのデータ入力(Input)のほかに、クロック信号と電源を供給してもらう。このクロック信号に合わせてデータの送受信を行なうのが同期回路なのだが、その要になるのが先頭にある「ラッチ」(Latch)である。ラッチとは「値を保持する回路」と考えればよい。Inputからの値は時間経過に応じて変化するが、Latchはクロック信号の立ち上がりのタイミングでInputの値を判断して、その値をラッチの出力として保持し続ける。このラッチの出力は、次のクロック信号の立ち上がりのタイミングまで、一切変化しない。なお、ラッチの先に実際の回路があるが、これらはクロック信号を使わない。

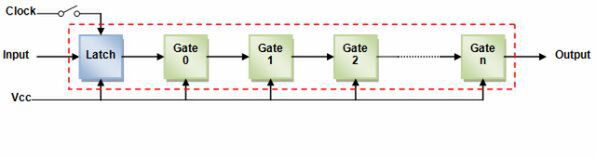

クロックゲーティングとは図4のように、ラッチへのクロック信号の供給回路にスイッチを挟み込むことで、ラッチへのクロック信号の供給を止められるようにする仕組みである。クロック信号の供給を止めると、ラッチはクロック信号の立ち上がりを検知できないので、ラッチから出力される信号は変わらないままとなる。そうなると「Gate 0」への入力が変化しないので、Gate 0の出力(=Gate 1の入力)も変化がなくなり、結局Gate nまでが一切変化しなくなる。

この「変化がない」というのが、CMOS回路では非常に重要である。CMOSでは電圧で状態を保持している。例えば「High」なら2V、「Low」なら0Vになる場合、「HighからLow」や「LowからHigh」といった変化があると、電圧が0Vから2V、または2Vから0Vに推移することになる。この推移の際には、どうしても電流が流れることになる。これがCMOS回路の動作時消費電力(Dynamic Power)と呼ばれるものの正体である。クロックゲーティングにより動作が止まると言うことは、どのゲートもまったく状態が変わらなくなるので、動作時消費電力は「0」になるというわけだ。

余談になるが、CMOSの前に広く使われていた「バイポーラ回路」の場合、状態を「電流」で保持していた。Lowなら0A、Highなら10mAという仕組みだ。この場合、状態がLowのまま保持されれば電流は流れないが、状態がHighのまま保持されると電流が流れっぱなしになってしまい、電力消費を減らせない。クロックゲーティングはあくまで、CMOS回路にのみ使える技法である。

この連載の記事

-

第776回

PC

COMPUTEXで判明したZen 5以降のプロセッサー戦略 AMD CPU/GPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 -

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ - この連載の一覧へ