クロックゲーティングの導入への課題とは?

話をBaniasに戻すと、原理的には簡単なクロックゲーティングであるが、実装はそう簡単ではない。CPU黒歴史の「Prescott~Tejas」でも触れたが、ほとんどのCMOS回路はダイナミック回路を使って構成されており、これはBaniasも例外ではない。そしてダイナミック回路は最低動作周波数が決まっているので、クロックゲーティングはこれに引っかかってしまう。

つまり、クロックゲーティングによりあるブロックへのクロック信号を一度遮断すると、再び復帰させても回路の状態が不定になってしまい、そのままでは動作を再開できないことになる。対策としては、そのブロックへのクロック信号を復帰させる際に、同時にそのブロックのみをリセットすればいい。ところがこのリセットに時間を食うと、復帰まで時間がかかってしまうので性能面への悪影響が大きい。

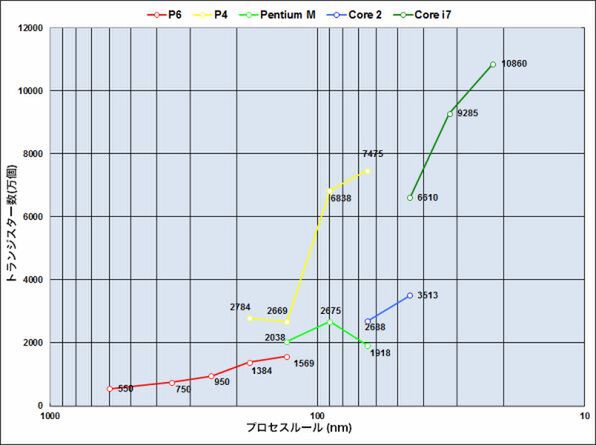

クロックゲーティングの技法そのものは以前から知られていたが、Banias以前のx86プロセッサーでこれを実装した製品がなかったのは、このあたりの細工がかなり複雑だったから、ということになる。連載161回で掲載した下のグラフで、P6コアとPentium Mコアを比較した場合、明確にトランジスター数が増えている理由のひとつは、このクロックゲーティングの細工※1に、それなりのトランジスター数を費やしたからだろうと想像される。

※1 単にクロック信号の遮断と復帰のみならず、復帰時のリセットの仕組みも必要になる。

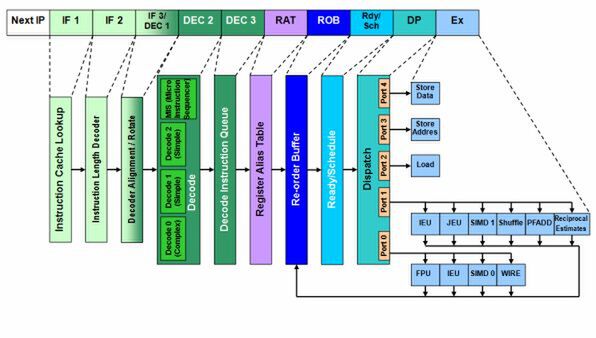

Baniasに続き2004年には、改良版の「Dothan」が投入された。Dothanの内部構造は図1のままで、2次キャッシュを増量した以外の違いはない。インテルはこの時期、その次の「Yonah」に向けて、内部構造の大幅な改良を進めていた。それは単にYonahだけではなく、その先の「Merom」世代も見据えたものであり、これだけの改良はいかにインテルであっても、Baniasの出荷から1年でできるようなものではなかった。

DothanはYonahが登場するまでのピンチヒッターとして、プロセスの微細化による高速動作と、2次キャッシュ大容量化による性能改善を主な特徴として投入されたわけだ。Yonah世代ではどんな改良が加えられたのかは、次回に解説しよう。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ