一方の実行段であるが、こちらはスレッドごとに独立している構造だ。「SMT」(同期マルチスレッディング)は、例えば古くはPentium 4、最近で言えばNetLogic Microsystemsの「XLP Processor」のように、実行ユニットの利用効率が悪い場合には性能改善の度合いは大きい。

Pentium 4の場合は、実行ユニットの利用効率は30%程度とインテル自身が明言しており、これがハイパースレッディング・テクノロジーの利用により50%程度まで改善した。NetLogic XLPの場合は、当初からSMTの利用を前提として、MIPS64ベースで4命令同時実行のスーパースカラー構成となっている。こちらもシングルスレッドでの実行段の利用効率は低そうだ。

またメモリーアクセスへの遅延が大きなシステムでは、SMTによってあるスレッドがメモリーアクセス待ちの間に、別のスレッドの処理を進める形で効率を改善できる。ところが逆に、すでに実行ユニットの利用効率が十分高い場合には、SMTでの性能改善の度合いはそれほど多くない。むしろオーバーヘッド増加により性能が下がる場合すらある。

例えばCore i7の場合、32bitのWindows XP環境ではハイパースレッディングを有効にすると、多くのケースで性能が落ちる羽目になる。こうした実情を考慮して、Bulldozerでは完全に異なる2つのコアに分離することで、確実な性能改善を図ったわけだ。

もちろん、例えば実行ユニットをALU×4・AGU×4にして無理やり1コア、という方法論もある。だが、それではスケジューラーやレジスタファイルなどを含めて、内部が複雑になりすぎるだろう。物理的に2つのコアに分離するのは、デザインの面からは理にかなっていると言える。

共用化されてもFPU性能は落ちない?

一方共用となったFPUであるが、以前にAMDのサーバー/ワークステーション製品担当マーケティングディレクターであるジョン・フリー(John Fruehe)氏に確認したところ、「(Phenom IIなどと比較して)性能が落ちることはない」と明言していた。フリー氏は「MMX/SSEに関しては4命令/サイクル、AVXに関しては1命令/サイクルで実行可能。コアあたりの性能という観点で見れば、従来のPhenom IIと同じピーク性能である」と述べる。そのため科学技術計算向けの用途であっても、従来のK10ベースOpteronと比べて性能が下がることはない、という。

もうひとつの共用部である2次キャッシュだが、特筆すべきはサイズよりも、やたらと大きなTLBや、最大23ものキャッシュミスの同時フィルを可能にするメモリーサブシステムとの連携だろう。このあたりはデスクトップ向けというよりも、Opteron向けに効果的な対応に思える。

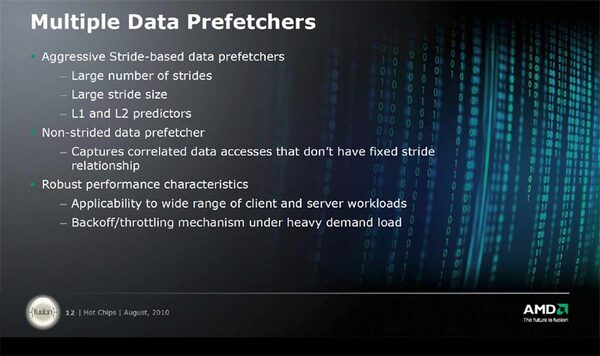

そのほかにもIPC(Instructions Per Cycle)改善として、命令プリフェッチやデータプリフェッチの改良なども挙げられている。命令プリフェッチに関しては「Phenom IIから小変更」といった程度で、むしろデータプリフェッチの方が大きく手が入っている印象がある。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ