年末年始特別編3

2011年の新CPUコア「Bulldozer」「Bobcat」の姿

2010年01月11日 12時00分更新

明らかにされた情報から、Bulldozerの姿を読み解く

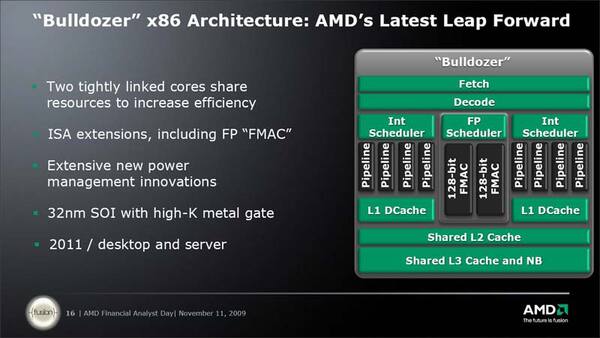

年末年始スペシャルの最後は、いよいよAMDの次世代コア「Bulldozer」「Bobcat」である。2009年11月に開かれた「Financial Analyst Day」でBulldozerの詳細が発表された直後から、いろいろな議論がネット界隈で駆け巡った。

まずAMDが公開した話をまとめると以下のようになる。

- 2つのスレッドを同時に実行できるが、SMT(Symmetric Multi-Threading)とは異なり、整数実行ユニットはスレッド間で共用されない。

- 整数演算は4命令のアウトオブオーダー。また2ロード/サイクルをスレッドごとに実現する。

- 浮動小数点演算は2スレッドで実行ユニットを共用する。

- FMAC4 & CVT16をサポートする。

問題はこの「4命令のアウトオブオーダー」の解釈である。当初、筆者はBulldozerはスレッドごとに4つの「ALU+AGU(ロード/ストアユニット)パイプ」を持つと理解した。後述するBobcatのプレゼンテーションが、ALUとロード/ストアで実行ユニットの表記を変えているのに対し、Bulldozerではスレッドごとに4つの「パイプライン」が並んでおり、これは均質なものに見えたからだ。

また、K6世代の2命令/サイクルから、K7→K8→K10と3命令/サイクルを狙ったアーキテクチャーを3世代にわたって改良してきているので、「次は4命令/サイクルを狙っても不思議ではない」と考えていた。しかも、ローエンドのBobcatが2命令/サイクルのアーキテクチャーで出てきており、K10と合わせれば2/3/4命令/サイクルのアーキテクチャーが揃う形になる。

ところが、これに関しては日本AMD経由で米AMDより、明確に「スレッドあたりALUが2つ、AGUが2つの合計4つである」という回答が帰ってきた。つまりIPC(命令/サイクル数)的にはちょっと逆戻りした感がある。だが、もう少し上の回答を突っ込んで考えると、もう少し深い狙いがある事が見えてきた。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ