米インテル社が主催する開発者向け国際会議「Intel Developer Forum Shanghai 2008」(以下IDF上海)が2日に開幕した。初日の基調講演では、インテルの新しいCPUやプラットフォームに関するアナウンスが集中して行なわれた。

ここでは、同社上級副社長兼デジタル・エンタープライズ事業本部長のパット・ゲルシンガー(Patrick P.Gelsinger)氏による、次世代CPU「Nehalem」に関する基調講演についてお伝えしたい。

コア数バリエーションの増えるNehalem

今秋以降にリリースされる予定のNehalemは、サーバーやワークステーション、あるいはハイエンドデスクトップ分野向け製品から登場する。メインストリームのデスクトップ用Nehalemは、2009年の登場になる。

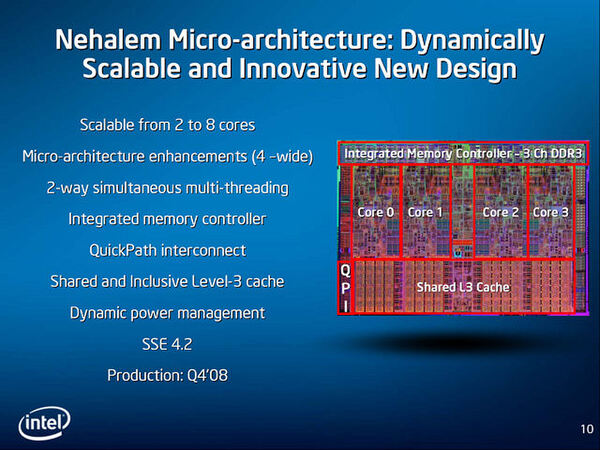

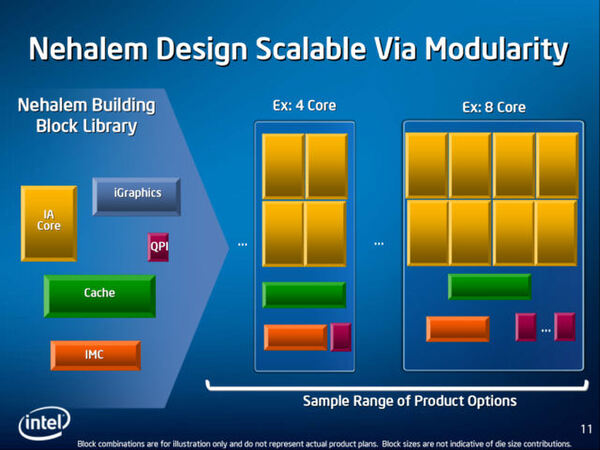

NehalemはCPUの設計自体を大きく変え、コア数を増設できるようにしている。このためNehalemでは、2、4、8コアのバージョンが用意される。既存のCore 2 Quad(コード名Yorkfield)では、Core 2 Duo(コード名Wolfdale)のCPUコア2つをひとつのパッケージに入れることで、クアッドコアCPUを実現している。しかし、Nehalemではコアの設計を大幅に変えて、コアをひとつずつ追加できるモジュラー構造となっている。

ちなみに、競合である米AMD社は3コアのPhenom X3プロセッサーを発表しているが、インテルでは中途半端なコア数のNehalemをリリースすることは考えていないようだ。

2008年中にリリースされるNehalemはサーバー/ワークステーション向けで、クアッドコアの製品からリリースされる。メインストリーム向けのデスクトップ版CPUは、クアッドコアとデュアルコアの製品が、価格別に用意されると思われる。またノートパソコンのCPUには、デュアルコア版のNehalemが用意される。

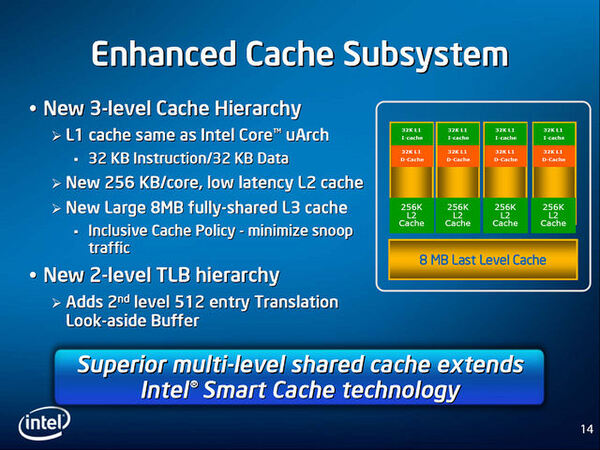

Nehalemのアーキテクチャーで最も大きな変更は、内蔵するキャッシュメモリーの構造だろう。Core 2 Duoでは2つのコアで2次キャッシュメモリーを共有していたが、NehalemではCPUコア個々に2次キャッシュメモリーを256KB(1次キャッシュは命令用32KB+データ用32KB)を搭載し、さらに複数のコアで共有する3次キャッシュメモリーが8MB搭載される。3次キャッシュの容量は、コア数が増えるほど増加できる。

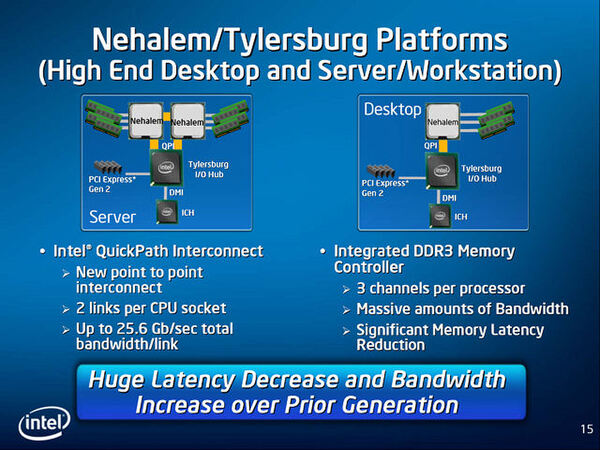

またNehalemでは、CPUにメモリーコントローラーが内蔵される。対応メモリーは、対応メモリーはDDR3-800/1066/1333のbufferedタイプ/Unbufferedタイプがサポートされる。メモリーチャンネル数は3チャンネル。1チャンネルあたりのメモリースロットは2スロット。Nehalemでは最大24GBまでサポートする。

メモリーコントローラーをCPUに内蔵したことで、チップセットも大きく変わる。Nehalemとチップセットを接続するインタフェースは既存のパラレルシステムバスではなく、新しいシリアルインタフェースの「QuickPath」が採用された。

さらにNehalemではPentium 4で採用されていた「Hyper-Threading Technology」(HT)と同じようなマルチスレッディング技術(SMT:Simultaneous Multi-Threading)が搭載されている。これにより、ソフトウェアから見るとクアッドコア版Nehalemは8コア(オクタルコア)のCPUとして動作する。

Nehalemのマイクロアーキテクチャー自体は、現行のCore 2 Duo(コード名Penryn)をベースとしており、小幅な改良となっている。その中でも大きめの拡張が行なわれているのはSSEだ。SSEはPenryn世代のSSE4.1から、SSE 4.2への進化している。SSE4.2では、XMLの解析を高速化する「STTNI」(String&Text New Instructions)、CRC32処理、POPCNT(データマッチを高速に処理する命令)などの新命令が追加されている。そのほかの新命令としては、インテルの仮想化技術「インテル バーチャライゼーション・テクノロジー」をさらに高速化する命令が追加されている。

Nehalemの詳細なパフォーマンスや消費電力、発熱量などは明らかにされていないが、アーキテクチャー的にはCore 2 DuoのPenrynから、さらに33%もの並列性の向上を成し遂げたとしている。

消費電力に関しては、実際にモノが出てくるまではなんともいえない面があるが、45nmプロセスの消費電力が、65nmプロセスに比べて順調に減っていることを考えれば、かつてのPentium 4のような熱いCPUになるとは思えない。