インテル(株)は28日、東京都内にて記者説明会を開催し、米インテル 上級副社長兼デジタル・エンタープライズ事業本部長のパット・ゲルシンガー(Patrick P.Gelsinger)氏が今後のプロセッサーやプラットフォームの展開について語った。

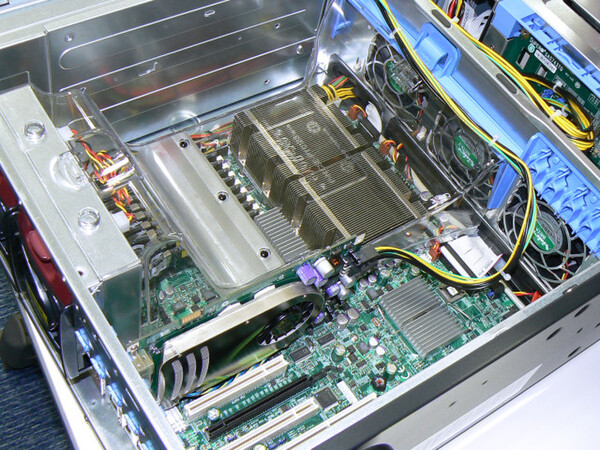

また、45nm製造プロセスを使用したサーバー・ワークステーション向けクアッドコアCPU「クアッドコア Xeonプロセッサー 5400番台」(コード名:Harpertown、ハーパータウン)搭載システムのデモも披露された。同CPUは今年11月には提供開始の予定。

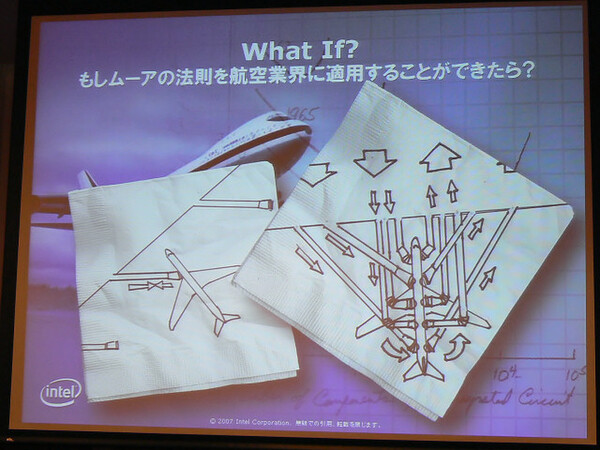

ゲルシンガー氏の講演は、9月に米国で開かれたハードウェア開発者向け国際会議「Intel Developer Forum 2007」(IDF)での発表内容を抜粋したもので、次世代のプラットフォームやCPU、I/O技術など非常に多岐に渡った。また、インテル最初のプロセッサーである「4004」(1971年登場)と同時期に登場した旅客機「ボーイング 747」を対比させて、ムーアの法則による半導体の進化の早さを示すといった趣向もこらされた。

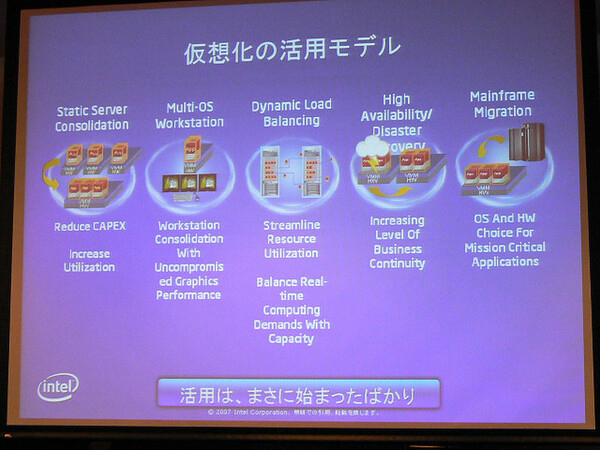

まずゲルシンガー氏は仮想化技術の進展について取り上げた。仮想化を大きな変化と位置づけ、サーバー統合や動的な負荷分散、メインフレーム並みの信頼性をPCサーバーにもたらすなど、さまざまな活用が始まっているとした。そして、CPUやチップセット、ネットワーク機能などで仮想化技術「インテル バーチャライゼーション・テクノロジー」(VT)をサポートするなど、仮想化に力を入れて開発を進めている点をアピールした。

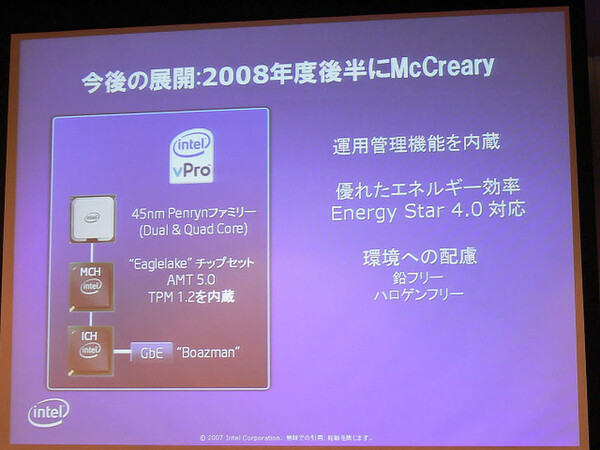

ビジネスクライアント向けプラットフォームについては、2008年に次世代のvProテクノロジー対応プラットフォーム「McCreary」(マクレアリー)を投入する。McCrearyは45nmプロセスを用いるPenryn世代のデュアル/クアッドコアCPUと「Eaglelake」(イーグルレイク)チップセットなどで構成される。EaglelakeにはTPM 1.2対応のセキュリティーチップの機能が統合されるという。TPM機能の統合と合わせて、ハードウェアによって暗号化処理を強化する「Danburyテクノロジー」(ダンブリー テクノロジー)も実装される。また、CPUやチップセットは完全鉛・ハロゲンフリーになるとして、環境への配慮にも言及した。

PCIe3、USB 3.0などI/O関連の強化も続々

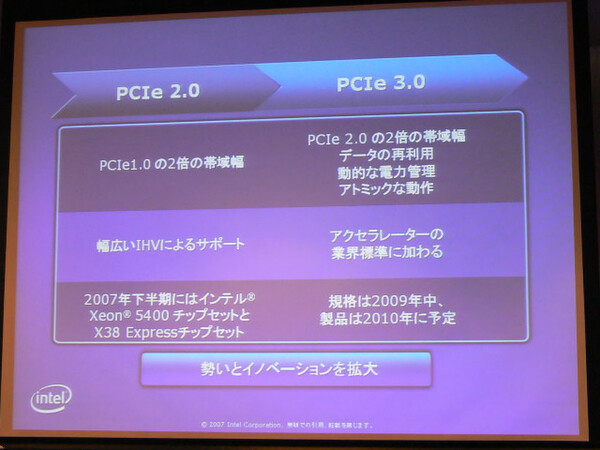

ゲルシンガー氏はサーバーからパソコンまで関わるさまざまなI/O技術の発展についても述べた。チップセットとその他のプロセッサー/デバイス類を接続するPCI Expressについては、2倍の帯域幅を持つ高速化された「PCIe 2.0」が、まもなく登場予定のX38 ExpressチップセットやXeon 5400番台向けチップセットで導入される。さらにPCIe 2.0の2倍の帯域幅を持つ「PCIe 3.0」も、2009年の規格化を目指して策定中という。PCIe 3.0はチップセットと各種アクセラレーターチップとのインターコネクト用途を対象としている。

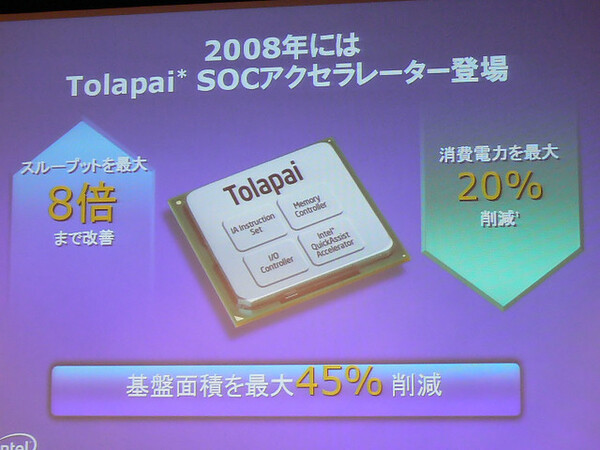

また、「QuickAssistテクノロジー」と称するCPUとアクセラレーターチップを接続する高速インターフェース技術を機器ベンダー向けにライセンス提供し、2007年中には対応機器が登場するという。さらに2008年には、半導体のダイ上でCPUとアクセラレーターをQuickAssistで結合したシステムオンチップ(SoC)「Tolapai(トラパイ) SOC アクセラレーター」も登場するという。

IDFで規格化推進グループの発足が発表された「USB 3.0」については、USB 2.0の10倍以上の性能と後方互換性の確保を目指し、2008年前半の規格化を目指して規格化を進めている。USB 3.0では銅配線だけでなく、光配線も対象とする規格となる。

そのほかにストレージ分野では、NAND型フラッシュメモリーを使用したSolid State Drive(SSD)に関して、「High Performance Solid State Driveテクノロジー」についても言及された。ゲルシンガー氏が「ストレージの革新的なテクノロジー」と呼ぶこの技術は、SSDをHDDより優れたストレージデバイスとするもの。SATA 3.0Gbpsのインターフェースに対応し、一般的なHDDと同形状をしているという。HDDの2倍以上の書き込み速度と、4.5倍以上の消費電力低減を実現するという。