久しぶりにAMD製CPUの話ということで、今回はISSCC 2025で説明されたZen 5コアの詳細を紹介していこう。Zen 5コアは、概略がCOMPUTEX TAIPEI 2024のレポート記事で触れられており、EPYCの周りの話は連載794回で説明している。ISSCCということもあり、物理実装や回路構成に関する、これまで説明がなかった内容も含まれていたので、それを説明する。

3種類の派生型があるZen 5

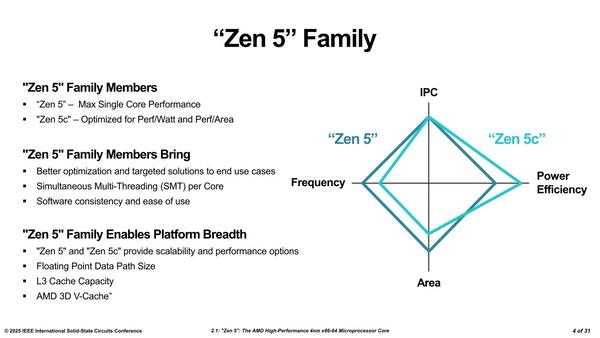

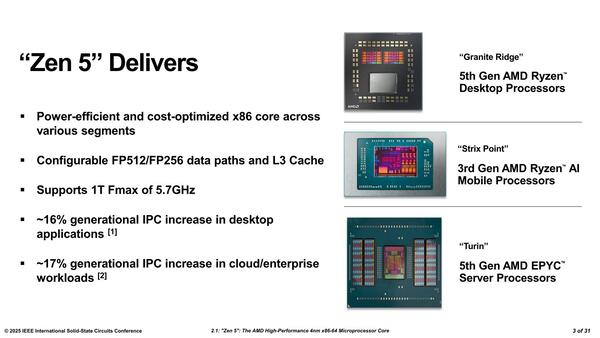

Zen 5世代は現時点で3種類の派生型がある。製品という意味ではデスクトップ向けのGranite Ridgeとモバイル向けのStrix Point、それとサーバー向けのEPYCの3種類ではあるのだが、まず物理実装でZen 5とZen 5cの差がある。

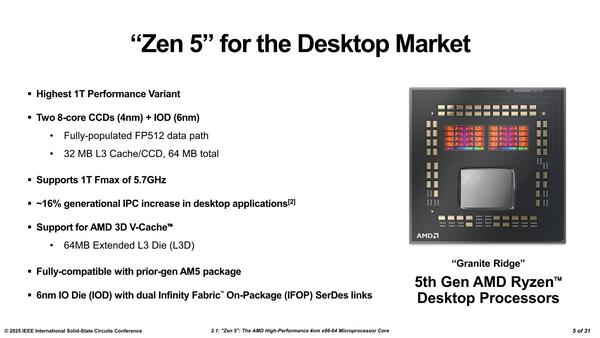

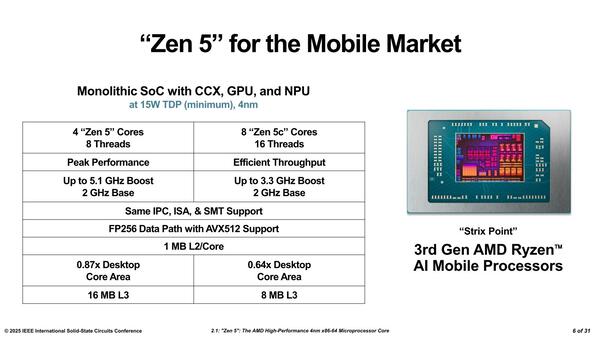

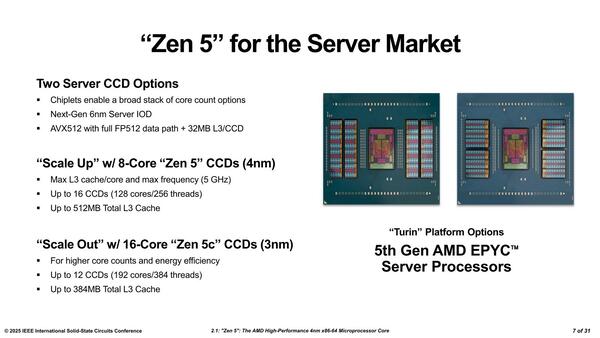

アーキテクチャーはZen 5と同じだが物理実装がZen 5とZen 5c、それとZen 5+Zen 5cのHybridの3種類ということになる。Granite RidgeがZen 5、TurinはZen 5ないしZen 5c、そしてStrix PointがHybridである

これはZen 4とZen 4cと同じで、論理的な構造は(L3のサイズを除くと)まったく同一である。異なるのは物理実装で、Zen 5が高速向けのCellライブラリーを利用しており、Zen 5cが省電力/高密度向けのCellライブラリーを利用しているという違いだ。

製品としてはGranite Ridgeが1ないし2つのZen 5 CCDと6nmのIODの組み合わせ、Strix Pointは4×Zen 5+8×Zen 5cをモノリシックとしたもの、TurinではGanite Ridgeと同じZen 5 CCDないし、(今のところは)Turin専用のZen 5c CCDを、新しく用意された6nm IoDと組み合わせる構成となっている。

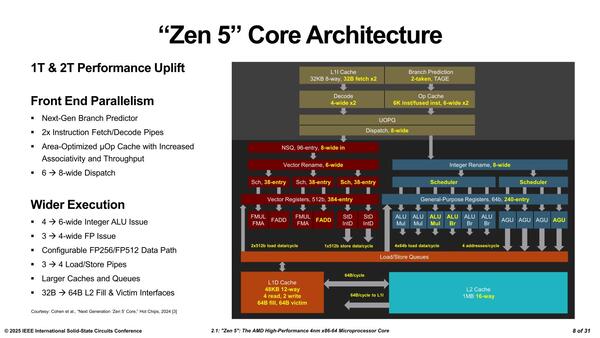

そのZen 5とZen 5cのCPUコアのブロック図が下の画像だ。このあたりまでの情報はすでに公開されている話である。

※お詫びと訂正:Strix Pointの説明に一部誤りがございました。記事を訂正してお詫びします。(2025年3月17日)

この連載の記事

-

第814回

PC

インテルがチップレット接続の標準化を画策、小さなチップレットを多数つなげて性能向上を目指す インテル CPUロードマップ -

第813回

PC

Granite Rapid-DことXeon 6 SoCを12製品発表、HCCとXCCの2種類が存在する インテル CPUロードマップ -

第812回

PC

2倍の帯域をほぼ同等の電力で実現するTSMCのHPC向け次世代SoIC IEDM 2024レポート -

第811回

PC

Panther Lakeを2025年後半、Nova Lakeを2026年に投入 インテル CPUロードマップ -

第810回

PC

2nmプロセスのN2がTSMCで今年量産開始 IEDM 2024レポート -

第809回

PC

銅配線をルテニウム配線に変えると抵抗を25%削減できる IEDM 2024レポート -

第808回

PC

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート -

第807回

PC

Core Ultra 200H/U/Sをあえて組み込み向けに投入するのはあの強敵に対抗するため インテル CPUロードマップ -

第806回

PC

トランジスタ最先端! RibbonFETに最適なゲート長とフィン厚が判明 IEDM 2024レポート -

第805回

PC

1万5000以上のチップレットを数分で構築する新技法SLTは従来比で100倍以上早い! IEDM 2024レポート - この連載の一覧へ

お気に入り

お気に入り