Xeon 6にはFCLGA4710以外のパッケージもあるらしい

ここからはXeon 6の話だ。8月25日からHotChips 2024が開催された。インテルはここでLunar Lake、Gaudi 3、Xeon 6、それと4TbpsのOpticalベースのインターコネクトについて発表した。このうちLunar LakeとGaudi 3に関してはあまり新しい話は見当たらなかった。問題はXeon 6で、タイトルは"Building for the Edge: The Intel Xeon 6 SoC"である。

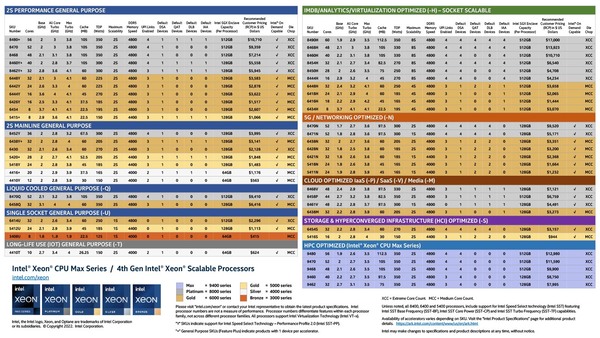

これは今だとXeon Dに相当する、通信機器など特定用途向けのXeonである。Sapphire Rapidsの世代では、連載702回で示した下の画像ようにコア数や動作周波数、利用できるアクセラレーターの数やTDPでラインナップを展開する形で、その意味ではXeon Dシリーズの直接的な後継製品は展開されなかった。

したがって、昨年リリースされたXeon D-2899NTはまだIce Lakeベースとなっているのだが、さすがにそろそろ更新の必要があると判断したのだろう。

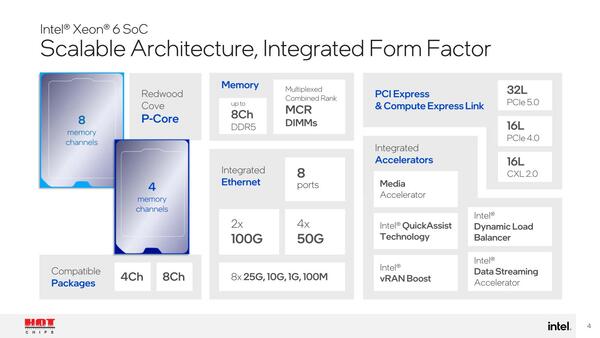

そんなXeon 6 SoCは、引き続きコンピュートタイルとIOタイルから構成されるが、このIOタイルがIntel 4で製造され、いろいろアクセラレーターが入った話が講演では示されたのだが、そちらは本題ではない。問題はパッケージである。

チップレット構造を取った関係で、パッケージそのものは少し大きくなるようで、基本的には既存のXeon 6700と同じパッケージが踏襲される「らしい」のはまぁ仕方がない。あとラインナップに8chメモリー以外に4chメモリーの製品も用意されるのも、ラインナップ的に考えれば不思議ではない。

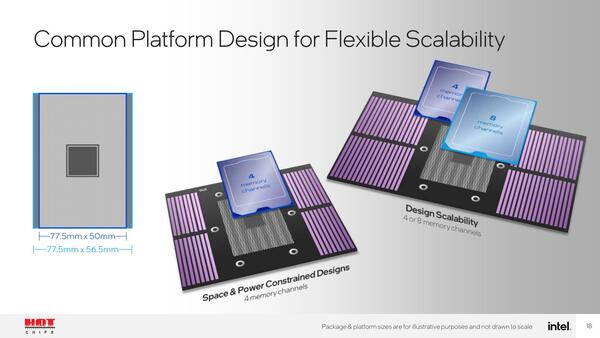

それはいいのだが、なんと4ch版と8ch版ではパッケージそのものが変わっていることが明らかにされた。4ch版の方はパッケージを6.5mm縮めるとともに、8 DIMMスロット構成とすることで幅を短くできる。一方8ch版の方は16 DIMMスロットになるので幅は広がることになる。

この4ch版と8ch版でパッケージの互換性があるというのは、8ch版の方で追加されている(というより削減されていない)片側4列づつの信号ピンは、追加の4chの信号線に割り当てられている。すなわち8chのデザインの方に4chのCPUを装着しても、ちゃんと動作するらしいのだが、「ここまで来てまだ新パッケージ作るのか?」とわりとインパクトがあった。

8chの方はすでに発表済のXeon 6と同じFCLGA4710と思われる。4chの方はランド数は正確には不明だが、おそらく4200~4300前後まで減るものと思われる。まさかこのランド数でBGAパッケージというわけにはいかないだろうから、当然ソケットを設けてそこに装着する形になると思われる。

DIMMスロットの本数の削減の方がはるかにサイズ削減には効果的なので、それに比べればパッケージによる面積削減の度合いは誤差の範囲だと思うのだが、それにもかかわらずここで幅50mmのパッケージを用意する理由が理解できない。既存の8chのパッケージを使いつつ4ch分は無効、ではいけなかった理由がわからないのが正直なところだ。むやみにラインアップを増やすのはいかがなものか。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ