信号ピンは19本しかないがコスト的な問題で

当時普及していた25ピンないし50ピンコネクターを使用

信号ピンは合計19本しかない。ただ実際には25ピンないし50ピンのコネクターが利用された。

| SACIの信号ピン仕様 | ||||||

|---|---|---|---|---|---|---|

| ピン | 信号 | |||||

| BSY | BUSY:SASIバスが利用中であることを示す | |||||

| SEL | 自分がInitiator(ホスト側)かTarget(デバイス側)かを示す | |||||

| C/D | Control/Data:デバイス側が、制御信号とデータのどちらを送受信するかを示す | |||||

| I/O | Input/Output:デバイス側が、送信と受信のどちらを行うかを示す | |||||

| MSG | Message:デバイス側が、メッセージ送信中であることを示す | |||||

| REQ | Request:デバイス側が、ACK信号と併せてハンドシェイクのために利用する | |||||

| ACK | Acknowledge:ホスト側が、REQ信号と併せてハンドシェイクのために利用する | |||||

| ATN | Attention:ホスト側が、Attentionコンディションをデバイスに伝えるために利用する | |||||

| RST | デバイスリセット中であることを示す | |||||

| SPARE | Spare:将来の利用のための予約。結局なにも使われなかった | |||||

| DB0-7+P | DB0~7がデータ(8bit)。奇数パリティ(DBP)が付加される | |||||

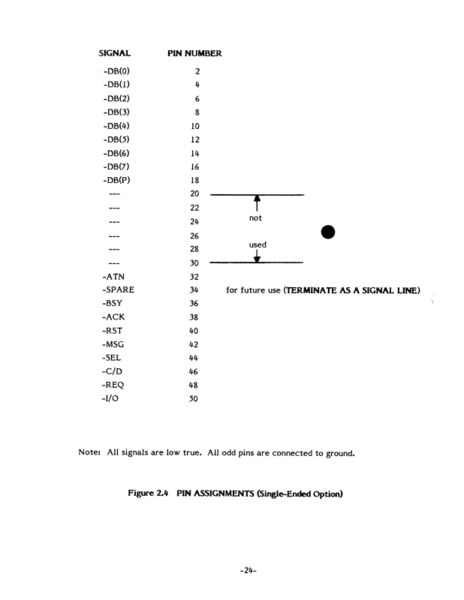

25ピンないし50ピンのコネクターが利用されたのはなぜか? というとそう規定されているためである。

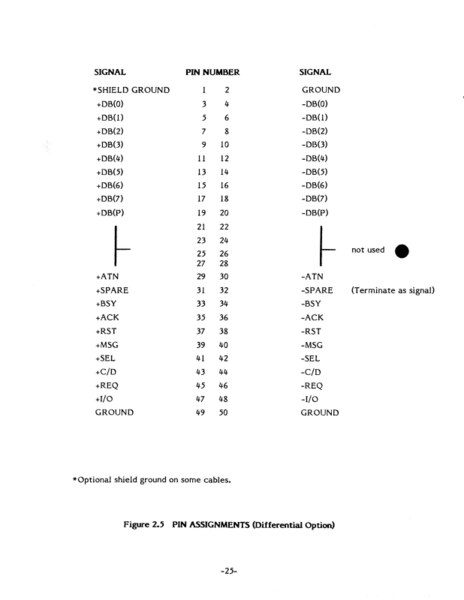

Differentialの信号もサポートされており、この場合前述のSA1403/SA1403DというSASI HDDコントローラーの2倍の信号線となる。あと両端(1~2/49~50)はGNDになっており、未使用ピンが4×2の8ピンとなっている

D-Subの25ピン、あるいは50ピンのRibbonコントローラーはこの規格が制定された1980年代に普通に入手できたので、これを流用するのがコスト的にも優れていると判断されたというあたりであろう。

ところでこれを見ても、複数台のFDDやHDDを接続する場合に、どう区別するのかがわからない。SASIはこの後出てくるSCSIと同じく(SASIを元にSCSIが作られたので、SCSIがSASIの仕様を引き継いだというのが正確だが)、機器ごとにIDを持っており、このIDで区別する仕組みとなっている。

ホストコントローラーはSASIバスの初期化の際に、それぞれのデバイスのIDを取得し、以後はこのバスIDを指定してデータを送受信する仕組みだ。このデバイスIDを取得するシーケンスは、Bus Arbitrationの機能が実装されているか否かで異なるが、そこまで細かい話も不要と思われるので割愛する。

デバイスのIDを取得するため、SASIの機器側には自分のIDを設定するためのスイッチ(ジャンパーだったりロータリースイッチだったり)が搭載されているのが普通である。ここで、他のデバイスのIDと重ならないように設定するのは利用者の仕事となる。なおこのデバイスのIDの事を、LUN(Logical Unit Number)と称する。

このSASI、信号レベルとしてはSingle Endedが最小2.5V/最大5.25V、Differentialは最小2.0V/最大5.25Vとなっており、5Vを利用するのが一般的だった。ケーブル長はSingle Endedの場合は最大6mで、Bus Stub(SASIのコネクターから、SASI/機器のコントローラーまでの配線)長は0.1m、Differentialではケーブル長が最大15m、Bus stub長は0.2mと規定されていた。

ケーブルそのものは50ピンのフラットケーブル、ないしねじった「より対線」を利用することとされ、コネクターは3MのScotchflex #3425-3000が推奨されている。

ただこのScotchflex #3425-3000は、カードエッジに刺すタイプのコネクターで、ケースの内部の配線はともかくとしてケース外の配線に使うには強度的に心もとない(ちょっと引っ張ると抜けてしまう)こともあり、外部接続の周辺機器には初期のSCSIと同じくロック付きの50ピンアンフェノールコネクターが使われることが多かった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ