今週のRISC-Vプロセッサー遍歴は、話を2020年頃に戻す。連載744回で触れた「RISC-Vに前のめりだった第1グループ」であるファブレスCPU IPベンダーはどんどん製品投入を開始している。わかりやすい例はSiFiveであろう。

CPU IPの提供だけでなくSoC全体の設計まで手がけるSiFive

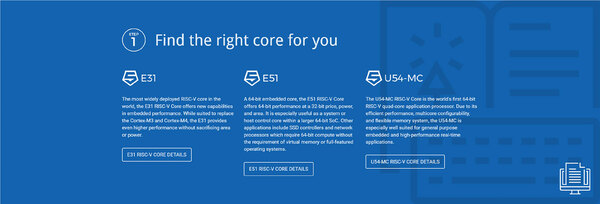

SiFiveの2017年10月における製品ラインナップが下の画像である。

E31は32bitのMCU向けで、競合製品はCortex-M3やM4とされ、シングルイシューのパイプライン構成ながら1.5 DMIPS/MHz(Cortex-M3/M4は1.25 DMIPS/MHz)の性能であり、28nmプロセスなら最大1.5GHzで動作するとされている。

もちろんこんなスピードで動かしたら普通はフラッシュメモリーが全然間に合わないので、実際にはもっと遅い周波数で動かすわけだが、逆に言えば28nmで1.5GHzということは90nmあたりでも数百MHzで十分回るわけで、これは高性能なMCUコアとして使うには十分である。

E51はE31を64bit対応にしただけという感じで、MMUもないので(PMP:Physical Memory Protectionユニットはあるが、これは俗にいうMPUである)、Linuxなども動かない。これはASIC内部のコントローラー向けといった扱いである。

この上位に来るのがU54-MCであるが、こちらはCortex-A53にもおよばない程度の性能でしかなく、アプリケーションプロセッサーとして使うには厳しい。ただソフトウェア開発用のプラットフォームとしては十分であり、とりあえずCPU IPベンダーとしての体裁が整ったという程度である。

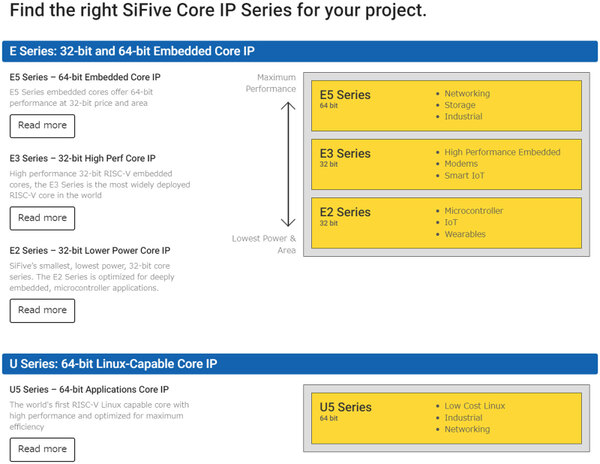

これが2018年になると、ローエンドにE2シリーズが追加される。

ちなみにこの時期、SiFiveは単にCPU IPのみならず、SoC全体を構築できるようなソリューションを提供している。というのは、SiFiveは2017年8月にOpen-Siliconという独立系のデザインハウス(ASICの設計を専門にした企業。顧客が論理設計を行なったチップの物理設計を担当したり、論理設計から物理設計まで担当して、テープアウトまで面倒を見たりする)を買収したことで、CPU IPの提供だけでなくSoC全体の設計まで手がけられるようになったからだ。

この時期SiFiveは“Processor Factory”、“Subsystem Factory”、“Chip Factory”という形で、単にCPU IPだけでなくCPUを含んだサブシステムの提供、あるいは最終的にASICそのものの製造まで意図していた。

結果から言えばこの試みは時期尚早であり、2020年にこのOpen-Siliconの舞台はOpenFiveとしてSiFiveの子会社の形で独立して動くことになり、2022年9月に英Alphawave IPに売却されることになった。

この手のサービスの場合、Armはデザインパートナーと呼ばれる認定を受けたデザインハウスが担っているが、SiFiveにはこうしたパートナーとなるデザインハウスが存在しない。したがって自前で抱え込もう、というのがそもそも上の画像の目論見だったように思う。

ただそのためには、顧客が使いたいと思うような魅力あるCPU IPが大前提であり、残念ながら当時のSiFiveのコアはそこまで魅力的と言えるほどではなかった。

結局のところOpen-Silicon部門は単独でもビジネスが成立する状態だったのに、SiFiveと組み合わせたことでビジネスが先細りになってしまったので、分離して運営(つまりArmなどをベースにしたASICの設計も担えるようにする)する形となり、こうなるとSiFiveが子会社として保持する意味がないので売却してしまった、というあたりだろう。

話を戻すと、E3コアは性能がそれなりにあり、性能/面積比や性能/消費電力比も良好と言っても、世の中にはそこまでの性能が要らないからもっと小さい回路規模で、というニーズが一定量存在する。Armで言えば、Cortex-M0やCortex-M0+、Cortex-M23あたりに該当するコアである。

2段のパイプライン構成ながら1.77 DMIPS/MHzと動作周波数あたりの性能はE30シリーズよりも若干上である。もっともその分動作周波数はあまり上げられないという制約は付くのだが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ