9月19日・20日にIntel Innovation 2023が開催され、初日の基調講演でPat Gelsinger CEOによりいろいろな情報が公開された。のっけから前回の情報の訂正からスタートしたい。

Sierra Forestはソケットあたり288コアだった

今年3月に開催されたDCAI Investor Webinarにおけるスライドでは、Sierra Forestは144コアという話であった。そしてHot Chipsにおける説明でも、1つのタイルに144コア(2ソケットで288コア)という説明がなされていた。

それもあって、前回の説明では、1つのコンピュート・チップレット+2つのI/O チップレットという構造が一番妥当に見える(そしてそのコンピュート・チップレットは8×5ブロックの可能性が高い)と説明をしたわけだが、いきなりこの前提がひっくり返された。

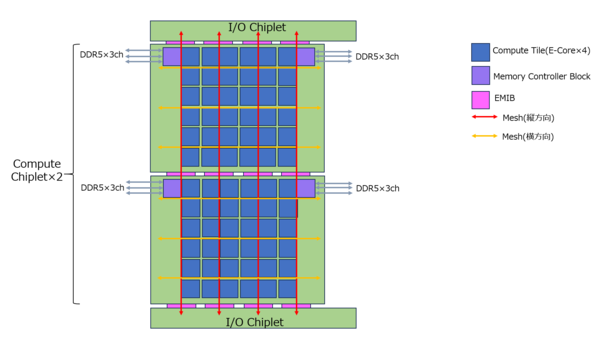

基調講演ではSierra Forestが2コンピュート・タイル構造で、しかもソケットあたり288コアであることが紹介された。つまりタイルあたり144コアなのは間違いないが、それが2タイルあるわけだ。

しかもSierra Forestは12chのDDR5を利用可能と説明された。つまりタイルあたり6chのDDR5のコントローラーを持つ計算になる。

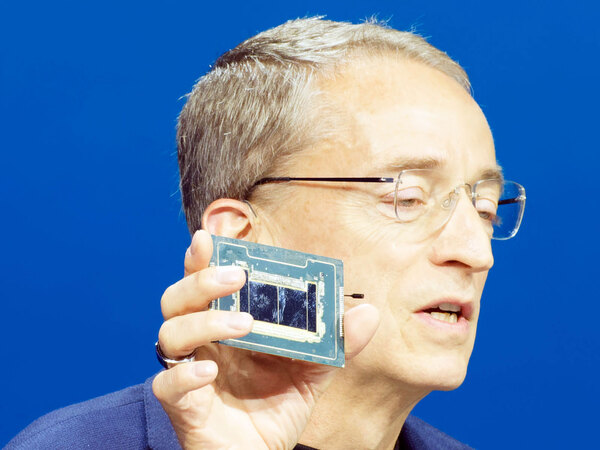

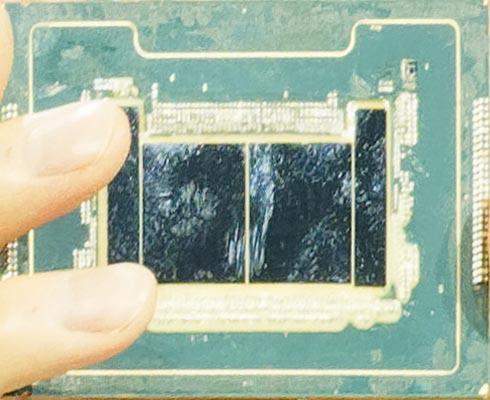

こうなると、144コアに関してはEコア×4のクラスターが36個、メモリーコントローラが3つという計算になる。また最初の画像を見ると、このスライドとは裏腹に、コンピュート・チップレットはパッケージの中央ではなく、偏りを持って配されていることがわかる。最初の画像のパッケージ部の歪みを補正したのが下の画像で、これを見るとCompute Tileの幅はI/O Tileの80%ほどである。つまり5:4の関係である。

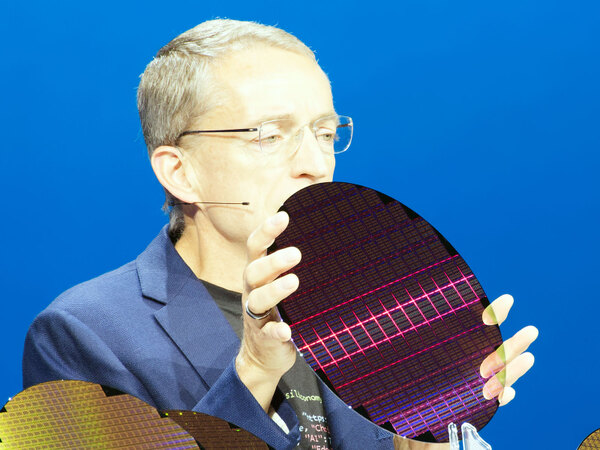

また今回Gelsinger CEOはSierra Forestのウェハーも公開した。ただこちらでは斜めからの撮影の関係で、ダイの構造がよくわからない。

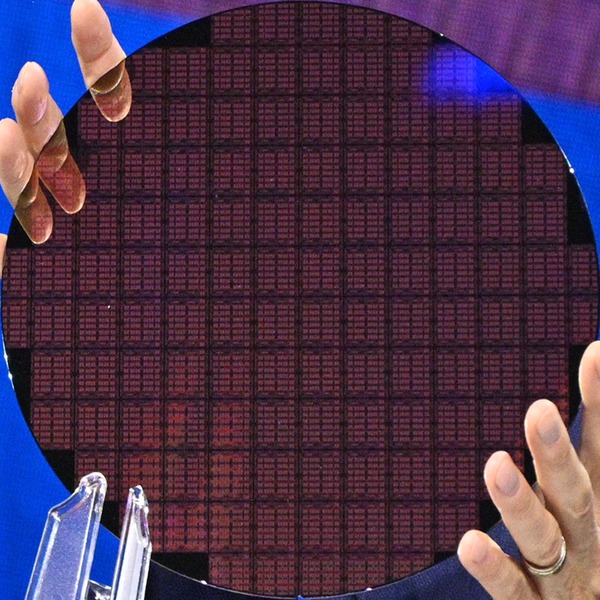

そこでインテル提供の正面からの写真をレタッチして縦横比を補正したのが下の画像である。

ここから4ダイ分を抜き出したのが下の画像だ。

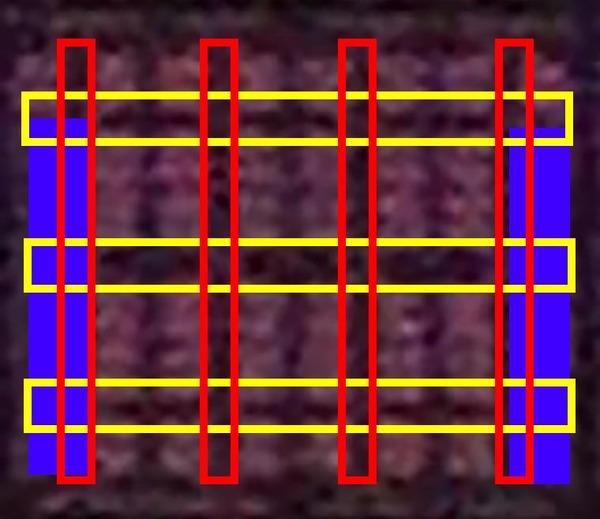

- 一番上のみ横が8ブロック。その下は6ブロック。縦方向は6ブロック分。

- 上の画像では、縦方向に4本、横方向に3本のメッシュが通っているように見える。

- コンピュート・タイルは6×6のブロックに集中しており、その左右にはみ出している2ブロックの下にあるのはPHYに見える

ここで、以下のことが想像できる。

- 赤:上下方向のメッシュ。これはEMIB経由でダイの外に接続される。

- 黄:左右方向のメッシュ。これはダイの中で完結する。

- 青:おそらくDDR5のPHY

ちなみにDDR5、従来のXeon Scalableでは1ブロックに2ch分のDDR5のI/Fが内蔵されているはずだが、このルールをそのまま適用するとDDR5用のコントローラーが3ブロック要る計算になる。

ただダイ写真を見る限り、全部で38ブロック分しかないあたりは、やはりSierra Forestでは1ブロックで3ch分のDDR5を制御できるようになっている、と考えるべきだろう。

結果として、正しい(?)Sierra Forestの構造図は下図になるだろう。

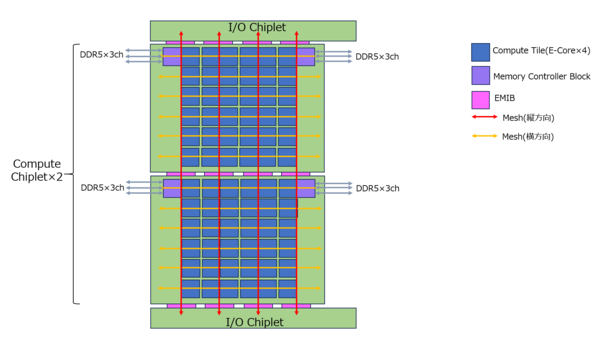

あるいは実際には横方向のメッシュは下図のようにチップレットあたり6本かもしれない。

一方縦方向は4本と思われる。これはGranite Rapidsの場合も縦方向は5本で、それがSierra Forestなどでは4本になると想定される。

そのSierra Forestのダイサイズはダイ写真を見る限り、22.34×26.53mm=592.68mm2ほどになる。ほぼ600mm2ということで、かなり大きいのは間違いない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ