Meteor LakeのE-Coreに実装成功

配線層が簡潔になり配線抵抗の削減にも効果あり

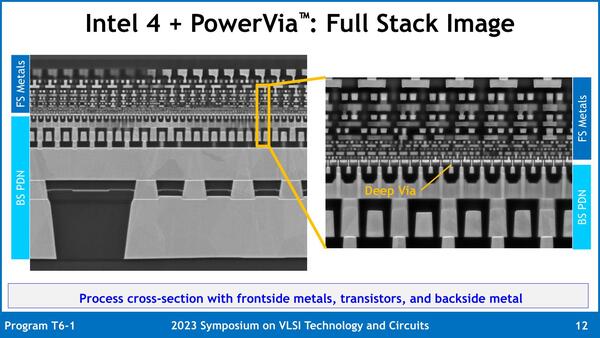

実際のIntel 4におけるPowerViaの構造の詳細が下の画像である。

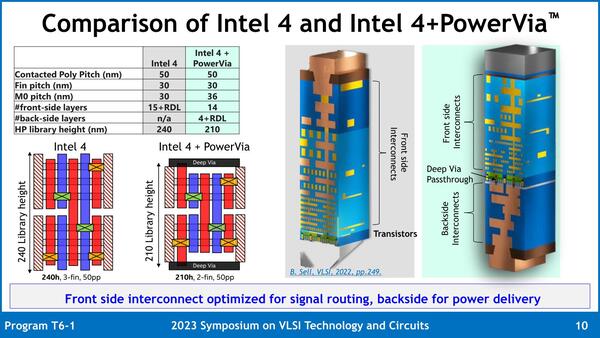

トランジスタに関しては「基本」PowerViaの有無は関係ない。「基本」というのは左の図を見てもらうとわかるが、トランジスタを上下から挟み込むようにDeep Viaというブロックが追加されている。またIntel 4は3 Fin構造でセルライブラリーを構成しているのに対し、Intel 4+Power Viaでは2 Finでの構成になっている。

今回はおそらくE-Coreのみでの実装なので、高速向けの3Finではなく高効率向けの2Finでのライブラリーのみを用意したのであろう。それともう1つ違うのはM0ピッチである。Intel 4では30nmピッチとなっていたM0だが、PowerViaを使うとPDNの配線が要らないため、36nmまで緩めても十分間に合うことになったと思われる。

トータルの配線層数はPowerViaなしが15層+RDL(Re-Distribution Layer)なのに対しPowerViaありだと18層+RDLと3層ほど増える結果になったのは、とりあえず今回は試作段階だからかもしれない。意外にFS側が減らなかったな、という印象である。

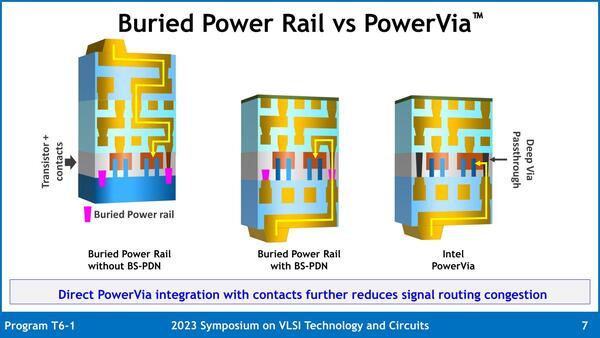

ところでDeep Viaの話だが、これはどうやってトランジスタそのものに電源を供給するか、という話に関係する。下の画像で一番左が従来型の電源供給方式、中央が一般的なBS PDNの方式、右がPowerViaである。

なにがDeepなのか? というと、おそらくBS側のPDNと接続するのがこのDeep Viaだから。ちなみに左側のDeep ViaはSource/Drainと接続されていないように見えるが、これは単に模式図だからで、奥で接続される構造になっているはずだ

つまり一般的な方式の場合、セルの外側にPDNからの配線を引っ張り、M0層を使って電源供給を行なうという方式である。これはBS PDNを使わない場合とトランジスタ層の互換性が一番高い。その反面、M0層を引き続きPDNに利用することになるので、M0層の配線密度を引き下げる効果が皆無になるし、ここが電源供給の際の損失の大きなポイントになりかねない。

そこでDeep Viaエリアから直接トランジスタに電力供給できるようにしたのが右側である。先のPowerViaの構造を示す画像でPowerViaを使う場合、トランジスタ上下のDeep Viaと赤いライン(Source)が接続しているのがわかるだろう。Deep Viaから直接ソースに電流を流しているわけだ。

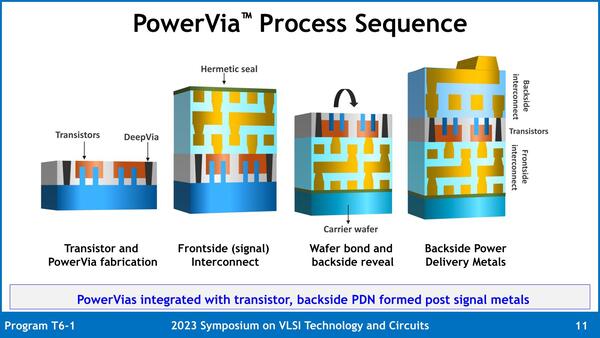

ちなみに製造方法は、まずトランジスタ→FS側を従来と同じように積層後、密閉シール層を被せてからひっくり返して改めてウェハーに載せ、その上にBS側を積層するという、シンプルな構成とのことである。

PowerViaの製造方法。これも簡単に見えるが、実はけっこういろいろ面倒なことは多い。インテルはこの製造方法について特許をいくつかすでに取得しており、そのあたりもあって詳細は説明しないつもりと思われる

下の画像がそのIntel 4+PowerViaの断面図である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ