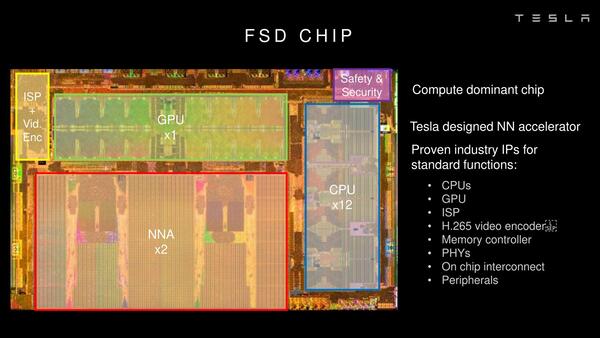

可能な限り市販のIPを利用して作られたFSD

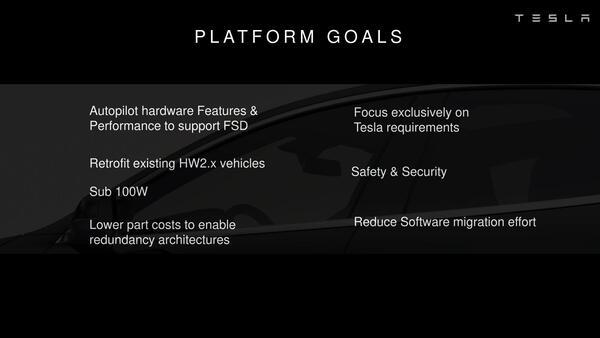

ということで長い枕になってしまったが、現状車載の自動運転向けプロセッサーはレベル2~3あたりをターゲットにしたものとなっている。まずFSDの設計目標が下の画像となる。

ここで“Retrofit existing HW2.x vehicles”というのは説明が必要だろう。Teslaは2008年から自動車の発売を開始しており、2014年には最初の自動運転用のハードウェア(HW 1.0)を搭載した。これが利用できるようになったのは2015年10月だ。

2016年にはHW 2.0がリリースされている。このHW 1.0/2.0はNVIDIAのプロセッサーを利用していたのだが、今回発表されたFSDを搭載するHW 3.0から自社設計/自社生産に切り替わった。ここの互換性というのは、まだHW 2.x台を搭載している旧来のTesla車を、HW 3.0にアップグレードすることを想定しているという話である。

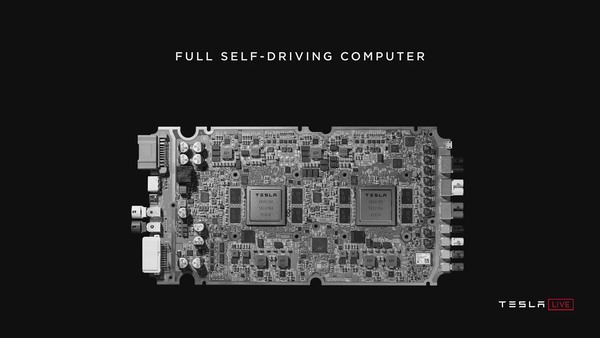

そんなFSDは下にある画像の基板で、2つのFSDチップが搭載されている。

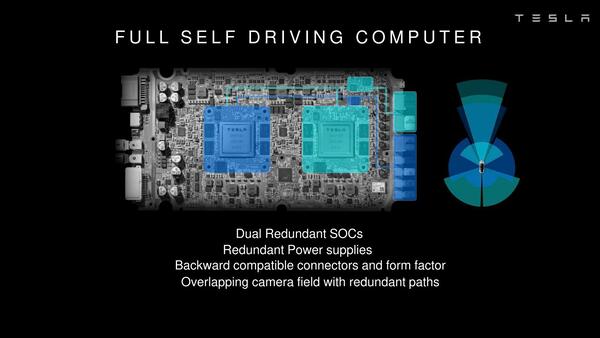

ただこの2のチップは冗長構成を取っており、電源やカメラからの入力もやはり冗長構成になっているので、片方のユニットや電源などがダウンしても問題なく処理を継続できるように配慮されているあたりはさすがに自動車向けである。

パッケージは37.5×37.5mmで、2116ボールのBGAと説明されている。

開発期間を短縮するためか、可能な限り市販のIPを利用しており、CPUは2.2GHz駆動のCortex-A72×12、GPUは16コア構成のもの、他にISPやビデオエンコーダー、PHYなども全部市販のIPを利用しており、Teslaが自前で設計したのはNNA(Neural Network Accelerator)とSafety&Securityのユニットのみと言ってもいい。

GPUは公表されていないが、時期および構成を考えるとMali-G71 MP16あたりではないかという気がする。ただ1GHz駆動で600GFlopsと発表されており、微妙に数字が合わない(G71だとスペック上は543.4GFlops)ので、もう少し動作周波数が上なのか、キャッシュなどの関係で性能が上がってるかのどちらかかと思われる。

ちなみにSafetyは2つのFSDを冗長構成(Lockstep動作)させるための制御回路であり、Securityは文字通りセキュリティ対策の部分である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ