今後はXilinxのリソースを使って

AIアクセラレーターを統合する予定

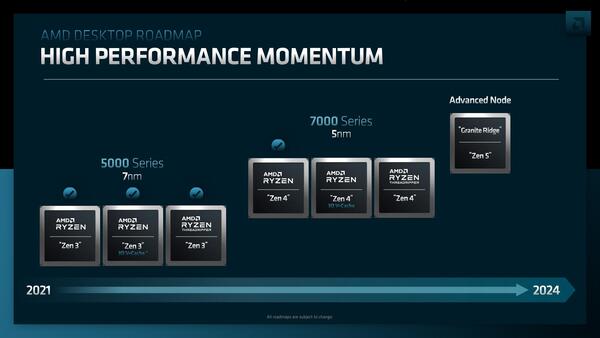

製品としてのRyzen 7000シリーズの特徴はここまで紹介してきたことですべてだが、製品ラインナップとしては5nm世代でZen 4とZen 4+3D V-Cache、それとZen 4ベースのRyzen Threadripperが用意されているという話であった。

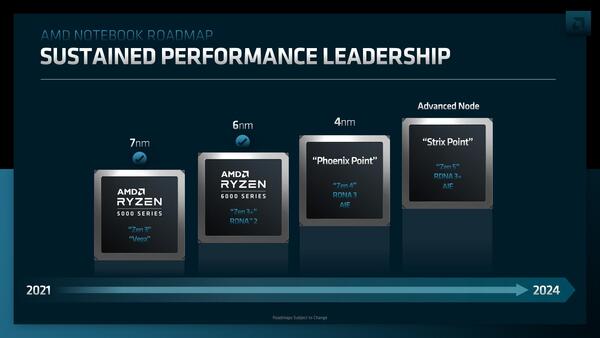

先にZen 4世代は5nmと4nmという話が出ていたが、デスクトップは5nmのままで推移することになる。では4nmは? というと、モバイル向けとなる。次世代のモバイルはZen 4コアとRDNA3、それにAIEを搭載し、4nmで製造されることになる。

モバイル向けロードマップ。余談だがTSMCはRibbon FETを採用した2nmプロセスの製造を2025年に始めるとしており、順序から言うとZen 5の次は2nmが視野に入るのだが、2025年はスマートフォン(というよりApple)と取り合いになるのが見えているだけに、どうするのか気になるところだ

その次のStrix Ppintは、Zen 5にRDNA3+、それにAIEを搭載する。先のPapermaster氏のCPUコアのロードマップ(2ページ目最初の画像)と照らし合わせると、このStrix Pointはおそらく3nmプロセスで製造されることになるだろう。

ところでここまで出てきたAIEとはなにか? という話だが、これはAI Engineの略である。前のページのZen 5に関するスライドに出てきた“Integrated AI and Machine Learning optimization”の正体がこれである。このAI Engine、もともとはAMDが買収したXilinxが2019年から出荷しているVersal ACAP(Adaptive Compute Acceleration Platform)で実装されているものである。

ACAPというのはFPGAの次のアーキテクチャーとして位置づけられているもので、「Versal ACAPというFPGA」と書くと怒られてしまうものだが、それはともかく。これはなにか? というとVLIWベースの演算エンジンの塊である。こちらは詳細が公開されているので、いずれAIプロセッサー連載の方で紹介する。

Versalという製品は6つのファミリーがあり、うち5つがすでに出荷中であるが、このうちVersal AI CoreとVersal AI Edgeという2つのファミリーにこのAIプロセッサーが搭載されている。

ちなみにハイエンドであるVersal AI Coreの場合、AI Engineが最大400個、またはAI Engine-MLが最大304個搭載され、これとは別にDSPが最大1968個やFPGA LUT(Xilinx用語ではLogic Cell)が158万6000個搭載されるなど猛烈な演算処理性能を持っている。で、Xilinx買収後にAMDはこのAI周りに関して新しい戦略を立てた。それがXDNAである。

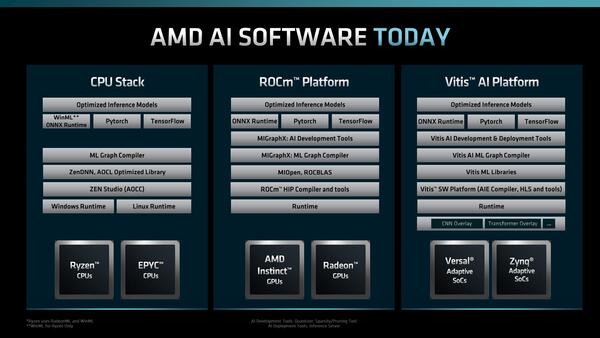

現状AMDは、Ryzen/EPYCは基本的にAI処理機能は装備されていない。RDNA/CNDAに関してはROCm経由でいくつかのAIフレームワークをサポート。一方XilinxベースのFPGAはVersal AI Core/Edge以外はAI用エンジンは搭載されていない感じで、まったくソフトウェアの共通性がない。

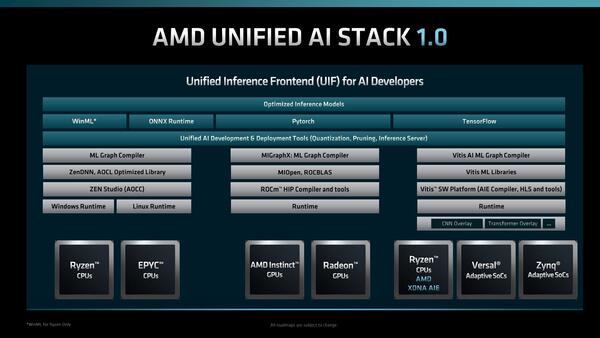

そこでまず、おそらくZen 4/RDNA3/CDNA3の世代に向けて、まずUnified AI Stack 1.0をリリースする。ただこの時点ではまだ上に皮を被せただけで、内部の共通化には至っていない。

Xilinxの買収は今年2月に完了したので、さすがにデスクトップのRyzen 7000シリーズには間に合わない。なので最初の搭載はモバイル向けのPhoenix Pointであり、すべてのCPUに入るのはZen 5世代からということになる

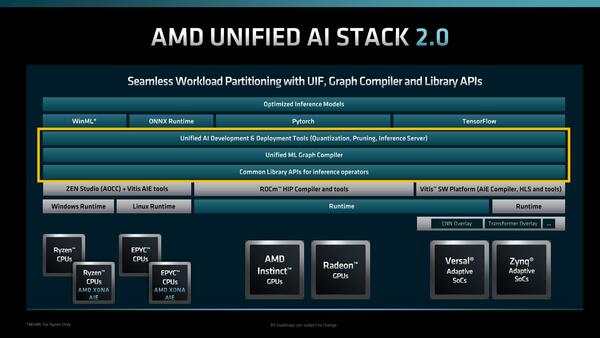

これがもう少し共通化が進むのは、Zen 5世代に投入されると思われるUnified AI Stack 2.0になる形だ。この頃になると、CPUとVersalで共通のAI Engineを搭載しており、これをベースに高効率にAI/MLの処理が出来るというのがAMDの目標と思われる。

この構図は、インテルがAI関連のソフトウェアAPIをOpenVINOとしてまとめ、さらにこれをoneDNN(oneAPI Deep Neural Network Library)として高レベルでまとめたのによく似ている。おそらくUnified AI Stack 1.0の段階でVNNIがサポートされ、2.0ではVNNIとAI Engineの両対応になると思われる。

単にCPUコアの更新だけでなく、Xilinxのリソースを使ってAIアクセラレーターまで統合する計画が明確に示されたのが今回のロードマップだったと言える。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ