Zen 4コアとZen 5コアのロードマップ

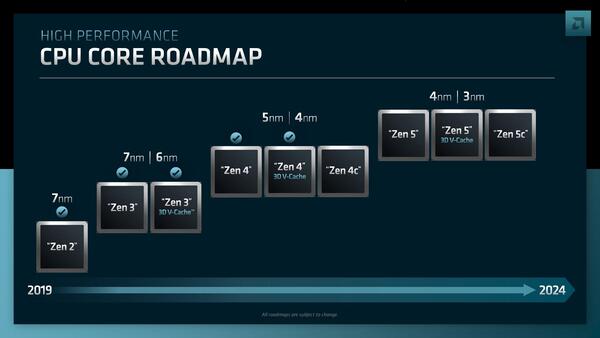

さてそれでは本題のCPUコアについて。Make Papermaster氏(CTO&EVP, Technology and Engineering)が示したCPUコアのロードマップが下の画像だ。

まずZen 4は5nmでスタートするが、後半には4nm製品も投入される。また当初のZen 4は3D V-Cacheなしだが、後追いで3D V-Cache付きも投入される。さらにクラウド向けにZen 4cも用意される。この図式はZen 5世代にも適用され、Zen 5とZen 5 3D V-Cache、それとZen 5cが提供されることが明らかにされた。

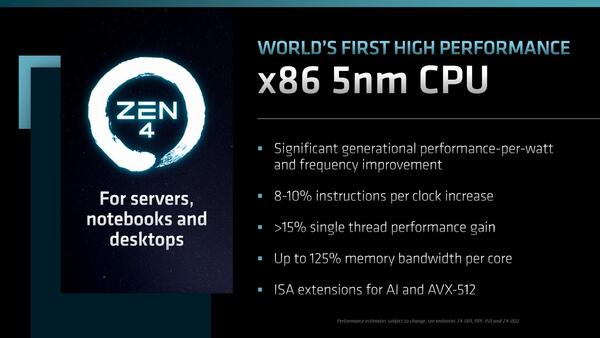

直近で興味があるのはZen 4コアであるが、特徴は下の画像の通り。IPCそのものはZen 3比で8~10%程度、とされた。ちなみに別のスライドで、Zen 4コアはデスクトップ・アプリケーションの場合のIPC向上は8%程度とされている。

Memory Bandwidthについては、単にメモリーコントローラーがDDR4→DDR5になっただけではなく、それに見合うだけロード/ストアーユニットが改良されたという意味に取れなくもないのだが、そこまで帯域あげても仕方がない気もする

連載669回で書いたように、IPC向上はやはり10%未満で、後の性能向上は動作周波数の向上で実現している格好だ。おそらくRyzen 7000の16コアモデルの場合、ベースクロックは3.7GHzあたりになっているものと考えられる。

それと予想通りAVX-512が搭載された。ISA extensions for AIはまだ未公開だが、これもVNNIと考えて間違いないだろう。新情報としては、動作周波数の向上とあわせ、消費電力の削減にも注力したとしていることだ。連載669回の最後で、TDPが170W、PPTは230Wに設定されていることをレポートしたが、これはあくまでもSocket AM5の最大供給量という話で、少なくとも最初に出てくるRyzen 7000シリーズはもっと省電力である可能性が出てきた。

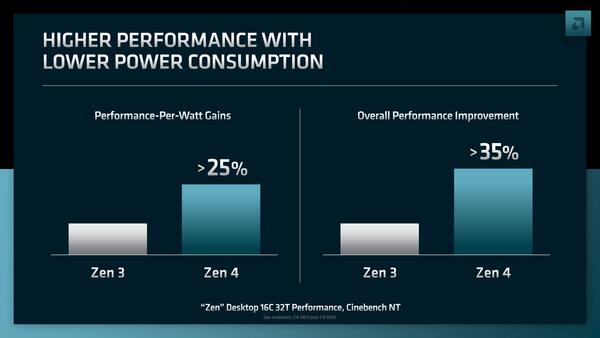

下の画像がその詳細である。CineBenchのnTでの比較であるが、CineBench nTの場合は処理時間が短い。Ryzen 5 5950Xの場合、昨年Alder Lakeとの比較対象で測定した時には31秒ほどで処理が終わっている。

この程度ではブーストが効きまくりの状態になるので、消費電力は定格の105Wではなく35%増しの141.75Wになる計算で、実際筆者の測定でもメモリーアクセスの分などと合わせて164.2Wという計測結果が出ている。実際にはフル稼働時のVRMでのロスなどもあるので、おおむね140W程度であろうと考えられる。

さて、Zen 4では性能が35%増し、電力効率は25%向上となっている。仮に消費電力が変わらないとすると、電力効率は35%向上するわけで、実際には消費電力の値そのものは8%程度増加していると考えられる。つまりCineBenchのnT動作時には153W程度。これはブースト時の値なので、定格でのTDPは113.4Wほどになるという計算になる。

省電力とは言い難いかもしれないが、少なくとも爆熱ではない。Base Power 125W/Maximum Turbo Power 241WのCore i9-12900Kよりはかなり現実的に使える値と思っていい。

実際上に書いたテスト中のCore i9-12900Kの消費電力は284.9Wに達している。ほぼ241Wの枠一杯まで消費電力を使い切ってることがうかがい知れる。連載669回の最後で「こちらもAlder Lakeに引けを取らない(?)発熱ぶりが期待できてしまうのは、やや残念である」と書いたが、これはとりあえずは杞憂に終わりそうである。

ところでIPCが8%程度の向上、ということは命令パイプラインそのものはZen 4からほとんど変わっていないと思われる。というのは2次キャッシュの倍増(512KB→1MB)やDDR5メモリーのサポートなどでそれぞれ2~3%程度の向上があるはずで、あとは細かな改良が行なわれた程度、と考えるのが妥当だろう。したがって、ダイサイズが異様に大きい理由は依然として不明であるが、それを除けば理解できる構成である。

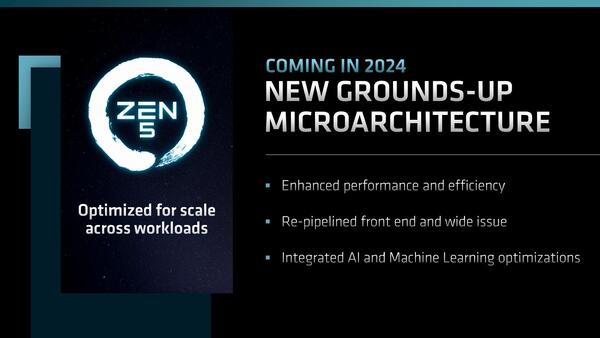

ではパイプラインの大幅な強化は? というと、Zen 5送りになった。こちらでは、フロントエンドとバックエンドのどちらもよりワイドになるとともに、パイプラインの再設計を行なったとある。

興味あるところだが、こればっかりはもう少し詳細が出てこないとなんとも言えない。とりあえず連載652回で示した5命令デコード/10命令発行のパイプラインは完全に間違っている、ということが確定したわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ