ロードマップでわかる!当世プロセッサー事情 第644回

業界初のマルチダイGPUとなるRadeon Instinct MI200の見事な構成 AMD GPUロードマップ

2021年12月06日 12時00分更新

連載635回でFrontierに納入される予定のRadeon Instinctの構成をいろいろ説明したが、“AMD Accelerated Data Center Premiere”では当然こちらの説明もあったので、答え合わせも兼ねてご紹介したい。

ちなみに発表記事で簡単にRadeon Instinct MI200シリーズの概要が紹介されているが、細かい製品仕様の話は最後にする。

1つのパッケージに2つのダイを搭載した見事な構成の

Radeon Instinct MI200シリーズ

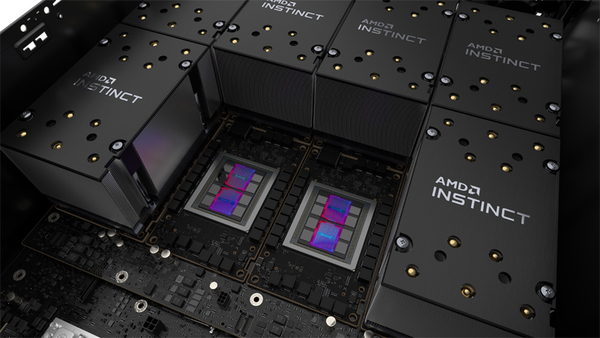

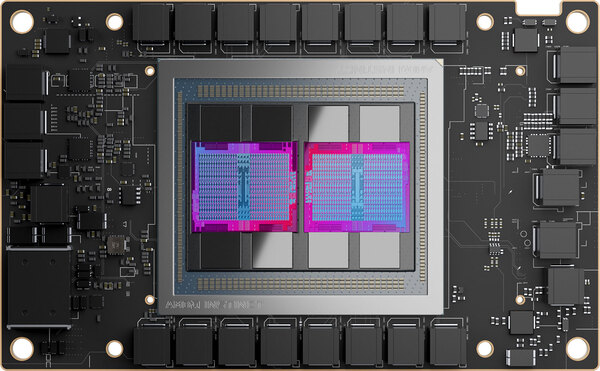

連載635回のノード構成推定図で「1つのRadeon Instinctと描いたものが、2つのRadeon Instinctを搭載したモジュールだと仮定すると、このギャップはもう少し縮まる」と書いたが、実際に発表されたRadeon Instinct MI200シリーズは見事に、1つのパッケージに2つのダイを搭載した構成となった。

フォームファクターはOAM(OCP Accelerator Module)準拠。OCP(Open Compute Project)はFacebook(現Meta)が主導する、標準的なサーバー向け仕様を策定するプログラムで、多くのメーカーがこれに参画しており、NVIDIAのA100もこのOAM仕様のものがメインである

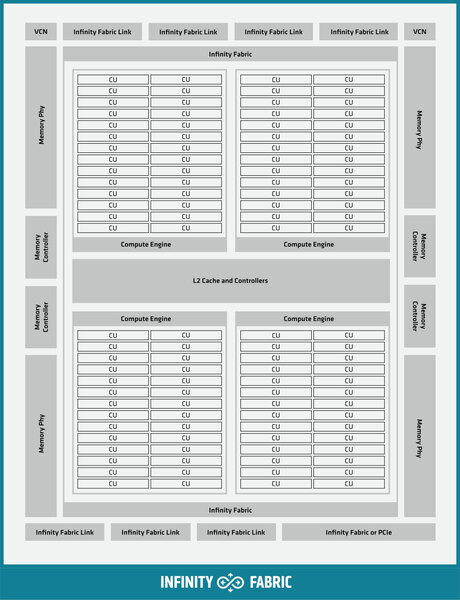

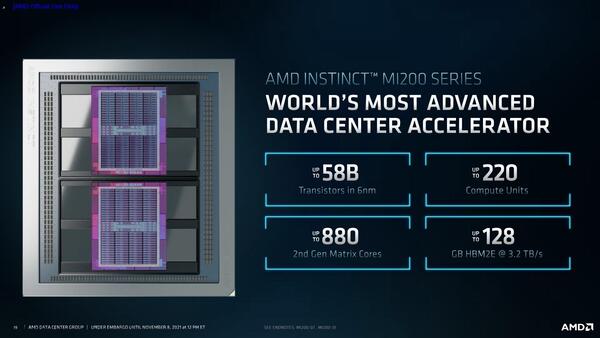

そのRadeon Instinct MI200シリーズの構成が下の画像だ。HBMはダイあたり4スタック、XCUはダイあたり110なので、実はRadeon Instinct MI100と比較すると、微妙にXCUの数が減っている計算になる。

HBM2eの寸法(9.975×10.975mm)から推定されるダイサイズは25.1×29.3mmで735.4mm2ほど。Radeon Instinct MI100の推定ダイサイズ(763.2mm2)とほぼ変わらない

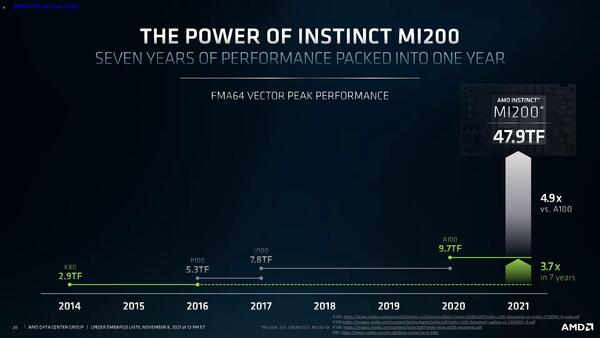

それにもかかわらず、FP64のベクトル演算性能が4倍ほどに引き上げられている。ダイ1つあたりの性能で言っても軽く倍である。

こちらはNVIDIAの製品との性能比較になっているが、Radeon Instinct MI100の性能はFP64で11.5TFlops、FP32で23.1TFlopsとされている

もう少し細かい数字が下の画像であるが、FP64のベクトル演算で47.9TFlops、FP64のマトリックス演算で95.7TFlopsというすさまじい数字を叩き出している。

rennsai635回でFrontierのノード(EPYC×1+Radeon Instinct×4)の性能を49TFlops程度と推定したが、実際にはMilan-Xを無視してRadeon Instinct×4だけでも191.6TFlopsに達しており、スペック表の数字が正しければ9000ノードにおけるピークで1.72EFlopsに達する。1.5EFlops以上、というFrontierの目標数値はわりと堅く実現できる格好だ。

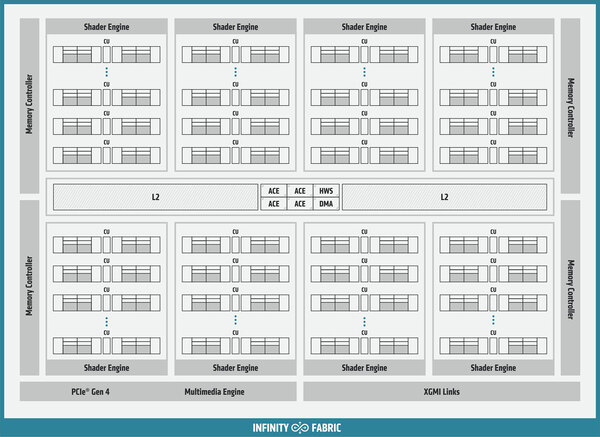

ではなぜこれが可能になったのか? という話であるが、MI100とMI200のダイの基本構成を比較するとわかる。

まずCU(CNDAからはXCUという呼び方に変わったが)の数そのもので言えば、MI100が16×8=128XCUで、うち8つを無効化して120XCU構成としている。一方MI200は14×8=112XCUで、うち2つを無効化して110XCUとしている格好だ。

細かいところでは、ACEがなくなったというか、これまではACEが任意のShader Computeに対してスレッドを割り振って処理する格好だったのが、どうもMI200ではACEが直接CUに対してスレッドを割り振るような格好で処理をすることになったようだ。このあたりの得失など、そのうちなにかしら話が出てくることを期待したい。

またHWS(HardWare Scheduler)のブロックもなくなっているが、これはCompute Engineにその機能が搭載されたのか、それとも全部ソフトウェアでスケジュールするようにしたのかも現時点でははっきりしない。

MI200の基本構成を見ると、一番上の左右にVCN(Video Codec Next)が搭載されているが、これはMI100にはなかった機能だ。このVCNではH.264/AVC、HEVC、VP9、JPEGのデコードと、H.264/AVC、HEVCのエンコードが可能とされている。

2次キャッシュのサイズそのものはMI100/MI200ともに8MBであり、16wayセットアソシエイティブ方式なのも同じであるが、MI100が64Bytes/サイクルなのに対し、MI200は128Bytes/サイクルと帯域が倍増されている。

メモリーI/Fが4組なのは同じだが、MI100はHBM2なので2.4GT/s、一方MI200はHBM2eで3.2TB/sとなっている。さらに、MI100にはXGMI Linksというポートが右下にあるが、これはInfinity Fabricのリンクのことだ。XGMIは“Socket/Inter-Chip Global Memory Interconnect”で、パッケージ同士の接続に利用されるものだが、MI100では最大4枚までのカードをRing Busの構成で接続できた。

一方MI200では後述するように、複数のダイ/パッケージ同士をPoint-to-Pointの形でInfinity Fabricで接続するため、MI200では外部向けに7ポートのInfinity Fabricと、1本のInfinity Fabric/PCIeポートが用意される格好になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ